- 1.65 MB

- 2022-04-29 14:15:00 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'全国高等学校“十一五”重点规划教材现代微型计算机原理与接口技术教程(习题解答)主编:杨文显副主编:杨晶鑫编著:黄春华胡建人宓双清华大学出版社

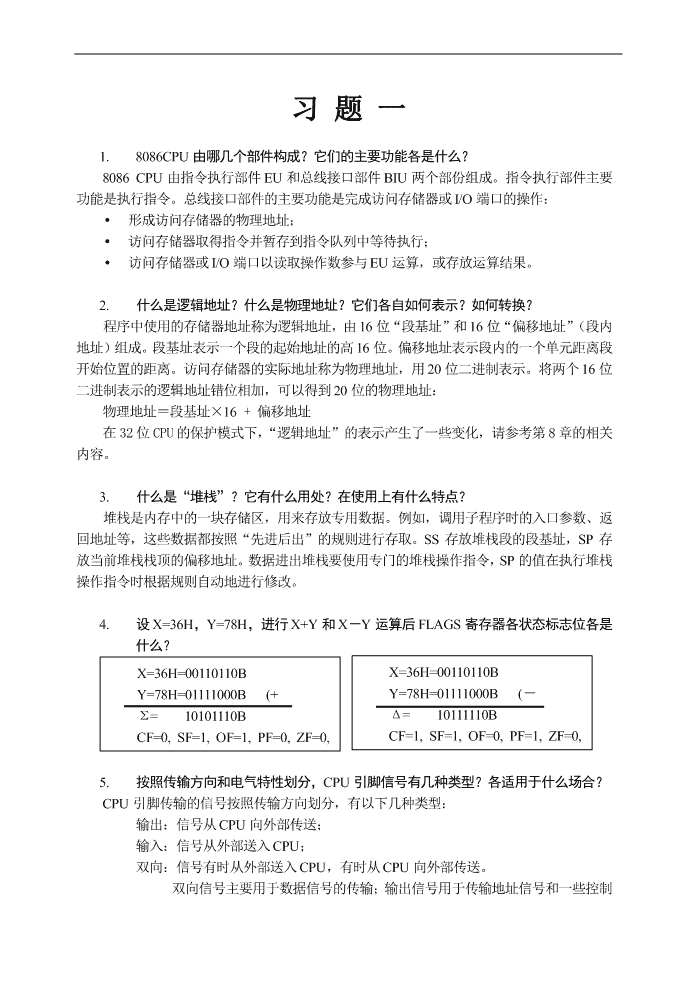

习题一1.8086CPU由哪几个部件构成?它们的主要功能各是什么?8086CPU由指令执行部件EU和总线接口部件BIU两个部份组成。指令执行部件主要功能是执行指令。总线接口部件的主要功能是完成访问存储器或I/O端口的操作:形成访问存储器的物理地址;访问存储器取得指令并暂存到指令队列中等待执行;访问存储器或I/O端口以读取操作数参与EU运算,或存放运算结果。2.什么是逻辑地址?什么是物理地址?它们各自如何表示?如何转换?程序中使用的存储器地址称为逻辑地址,由16位“段基址”和16位“偏移地址”(段内地址)组成。段基址表示一个段的起始地址的高16位。偏移地址表示段内的一个单元距离段开始位置的距离。访问存储器的实际地址称为物理地址,用20位二进制表示。将两个16位二进制表示的逻辑地址错位相加,可以得到20位的物理地址:物理地址=段基址×16+偏移地址在32位CPU的保护模式下,“逻辑地址”的表示产生了一些变化,请参考第8章的相关内容。3.什么是‚堆栈‛?它有什么用处?在使用上有什么特点?堆栈是内存中的一块存储区,用来存放专用数据。例如,调用子程序时的入口参数、返回地址等,这些数据都按照“先进后出”的规则进行存取。SS存放堆栈段的段基址,SP存放当前堆栈栈顶的偏移地址。数据进出堆栈要使用专门的堆栈操作指令,SP的值在执行堆栈操作指令时根据规则自动地进行修改。4.设X=36H,Y=78H,进行X+Y和X-Y运算后FLAGS寄存器各状态标志位各是什么?X=36H=00110110BX=36H=00110110BY=78H=01111000B(+Y=78H=01111000B(-Σ=10101110BΔ=10111110BCF=0,SF=1,OF=1,PF=0,ZF=0,CF=1,SF=1,OF=0,PF=1,ZF=0,AF=0AF=15.按照传输方向和电气特性划分,CPU引脚信号有几种类型?各适用于什么场合?CPU引脚传输的信号按照传输方向划分,有以下几种类型:输出:信号从CPU向外部传送;输入:信号从外部送入CPU;双向:信号有时从外部送入CPU,有时从CPU向外部传送。双向信号主要用于数据信号的传输;输出信号用于传输地址信号和一些控制

信号;输入信号主要用于传输外部的状态信号(例如READY)和请求(中断、DMA)信号。按照信号的电器特性划分,有以下几种类型:一般信号:用来传输数据/地址信号时,高电平表示“1”,低电平表示“0”;用来表示正逻辑的控制/状态信号时,“1”表示有效,“0”表示信号无效;用来表示负逻辑的控制/状态信号时,“0”表示有效,“1”表示信号无效。三态信号:除了高电平、低电平两种状态之外,CPU内部还可以通过一个大的电阻阻断内外信号的传送,CPU内部的状态与外部相互隔离,也称为“悬浮态”。CPU放弃总线控制权,允许其他设备使用总线时,将相关信号置为“悬浮态”。6.8086CPU以最小模式工作,现需要读取内存中首地址为20031H的一个字,如何执行总线读周期?请具体分析。为了读取内存中首地址为20031H的一个字,需要执行二个总线读周期。第一个总线周期读取20031H字节内容,进行的操作如下。T1状态:M/IO=1,指出CPU是从内存读取数据。随后CPU从地址/状态复用线(A19/S6~A16/S3)和地址/数据复用线(AD15~AD0)上发出读取存储器的20位地址20031H。为了锁存地址,CPU在T1状态从ALE引脚输出一个正脉冲作为地址锁存信号。由于需要读取高8位数据线上的数据(奇地址),BHE=0。为了控制总线收发器8286接受数据,DT/R=0。T2状态:地址信息撤消,地址/数据线AD15~AD0进入高阻态,读信号RD开始变为低电平(有效),DEN=0,用来开放总线收发器8286。T3状态:CPU检测READY引脚信号。若READY为高电平(有效)时,表示存储器或I/O端口已经准备好数据,CPU在T3状态结束时读取该数据。若READY为低电平,则表示系统中挂接的存储器或外设不能如期送出数据,要求CPU在T3和T4状态之间插入1个或几个等待状态Tw。TW状态:进入TW状态后,CPU在每个TW状态的前沿(下降沿)采样READY信号,若为低电平,则继续插入等待状态TW。若READY信号变为高电平,表示数据已出现在数据总线上,CPU从AD15~AD0读取数据。T4状态:在T3(TW)和T4状态交界的下降沿处,CPU对数据总线上的数据进行采样,完成读取数据的操作。第二个总线周期读取地址为20032H字节的内容。CPU发出的信号与第一个周期类似,区别在于T1状态CPU发出存储器地址为20032H,由于只需要读取低8位数据线上的数据(偶地址),BHE=1。在CPU内部,从20031H读入的低位字节和从20032H读入的高位字节被拼装成一个字。7.8086CPU有几种工作方式?各有什么特点?

8086/8088CPU有两种工作模式:最大工作模式和最小工作模式。所谓最小工作模式,是指系统中只有一个8086/8088处理器,所有的总线控制信号都由8086/8088CPU直接产生,构成系统所需的总线控制逻辑部件最少,最小工作模式因此得名。最小模式也称单处理器模式。最大模式下,系统内可以有一个以上的处理器,除了8086/8088作为“中央处理器”之外,还可以配置用于数值计算的8087“数值协处理器”、用于I/O管理的“I/O协处理器”8089。各个处理器发往总线的命令统一送往“总线控制器”,由它“仲裁”后发出。CPU两种工作模式由MN/MX引脚决定,MN/MX接高电平,CPU工作在最小模式;将MN/MX接地,CPU工作在最大模式。8.分析8086CPU两个中断输入引脚的区别,以及各自的使用场合。INTR用于输入可屏蔽中断请求信号,电平触发,高电平有效。中断允许标志IF=1时才能响应INTR上的中断请求。NMI用于输入不可屏蔽中断请求信号,上升沿触发,不受中断允许标志的限制。CPU一旦测试到NMI请求有效,当前指令执行完后自动转去执行类型2的中断服务程序。NMI引脚用于连接CPU外部的紧急中断请求,例如内存校验错,电源掉电报警等。INTR引脚用于连接一般外部设备的中断请求。9.什么是时钟周期、总线周期、指令周期?它们的时间长短取决于哪些因素?时钟周期:CPU连接的系统主时钟CLK一个周期的时间。CLK信号频率越高,时钟周期越短。总线周期:CPU通过外部总线对存储器或I/O端口进行一次读/写操作的过程称为总线周期。8086CPU总线周期一般由四个时钟周期组成,存储器/IO设备(接口)速度不能满足CPU要求时,可以增加一个或多个时钟周期。指令周期:CPU执行一条指令的时间(包括取指令和执行该指令所需的全部时间)称为指令周期。指令周期的时间主要取决于主时钟的频率和指令的复杂程度,它也受到存储器或IO设备接口工作速度的影响。10.在一次最小模式总线读周期中,8086CPU先后发出了哪些信号?各有什么用处?T1状态:M/IO指出CPU是从内存(1)还是从IO端口(0)读取数据。随后CPU从地址/状态复用线(A19/S6~A16/S3)和地址/数据复用线(AD15~AD0)上发出读取存储器的20位地址,对IO端口访问时从AD15~AD0上发出16位地址。为了锁存地址,CPU在T1状态从ALE引脚输出一个正脉冲作为地址锁存信号。如果需要读取高8位数据线上的数据(奇地址/读取一个字),BHE=0。为了控制总线收发器8286数据传输方向,DT/R=0。T2状态:读信号RD开始变为低电平(有效),DEN=0,用来开放总线收发器8286。T3状态:CPU检测READY引脚信号。若READY为高电平(有效),表示存储器或I/O端口已经准备好数据,进入T4状态;若READY为低电平(无效),表示存储器或I/O端口尚未准备好数据,插入一个或多个TW状态,直到READY变为高电平。

T4状态:在T3(TW)和T4状态交界的下降沿处,CPU对数据总线上的数据进行采样,完成读取数据的操作。11.结合指令‚OUT21H,AL‛,具体叙述最大模式‚总线写周期‛总线上的相关信号。T1状态:地址/数据复用线(AD15~AD0)上出现访问IO端口的16位地址21H。由于地址为奇数,需要通过高8位数据线访问端口,BHE=0。T2状态:IOW=0,表示本周期对IO端口进行写操作。地址/数据复用线(AD15~AD0)上出现来自AL的8位数据。T3状态:若READY为高电平(有效),表示I/O端口已经准备好接收数据。反之,表示I/O端口尚未准备好接收数据,需要CPU插入TW周期进行等待,直到READY出现高电平(有效)。T4状态:CPU结束本周期。

习题二1.内存储器主要分为哪两类?它们的主要区别是什么?内存储器分为随机存取存储器RAM(RadomAccessMemory)和只读存储器ROM(ReadOnlyMemory)两类。RAM中信息可以按地址读出,也可以按地址写入。RAM具有易失性,掉电后原来存储的信息全部丢失,不能恢复。ROM中的信息可以按地址读出,但是在普通状态下不能写入,它的内容一般不能被改变。ROM具有“非易失性”,电源关闭后,其中的信息仍然保持。2.说明SRAM、DRAM、MROM、PROM和EPROM的特点和用途。SRAM:静态RAM,读写速度快,但是集成度低,容量小,主要用作Cache或小系统的内存储器。DRAM:动态RAM,读写速度慢于静态RAM,但是它的集成度高,单片容量大,现代微型计算机的“主存”均由DRAM构成。MROM:掩膜ROM,由芯片制作商在生产、制作时写入其中数据,成本低,适合于批量较大、程序和数据已经成熟、不需要修改的场合。PROM:可编程ROM,允许用户自行写入芯片内容。芯片出厂时,所有位均处于全“0”或全“1”状态,数据写入后不能恢复。因此,PROM只能写入一次。EPROM:可擦除可编程只读存储器,可根据用户的需求,多次写入和擦除,重复使用。用于系统开发,需要反复修改的场合。3.已知一个SRAM芯片的容量为8K×8b,该芯片有一个片选信号引脚和一个读/写控制引脚,问该芯片至少有多少个引脚?地址线多少条?数据线多少条?13根据存储芯片地址线数量计算公式,k=log2(1024*8)=log2(2)=13,即总计有13根地址线。另有8根数据线、2根电源线。所以该芯片至少有25(=13+8+1+1+2)根引脚。4.巳知一个DRAM芯片外部引脚信号中有4根数据线,7根地址线,计算它的容量。k14根据存储容量计算公式S=2×I,可得该芯片的存储容量为:2*4=16K×4bit(位),也可表示为64Kb=8KB(字节)。5.32M×8b的DRAM芯片,其外部数据线和地址线为多少条?25根据存储芯片地址线数量计算公式,k=log2(1024*1024*32)=log2(2)=25,即需要25根地址线。但是,由于DRAM芯片的地址采用分时输入的方法,所以实际需要的地址线只有理论值的一半,此处为13根。数据线8根。

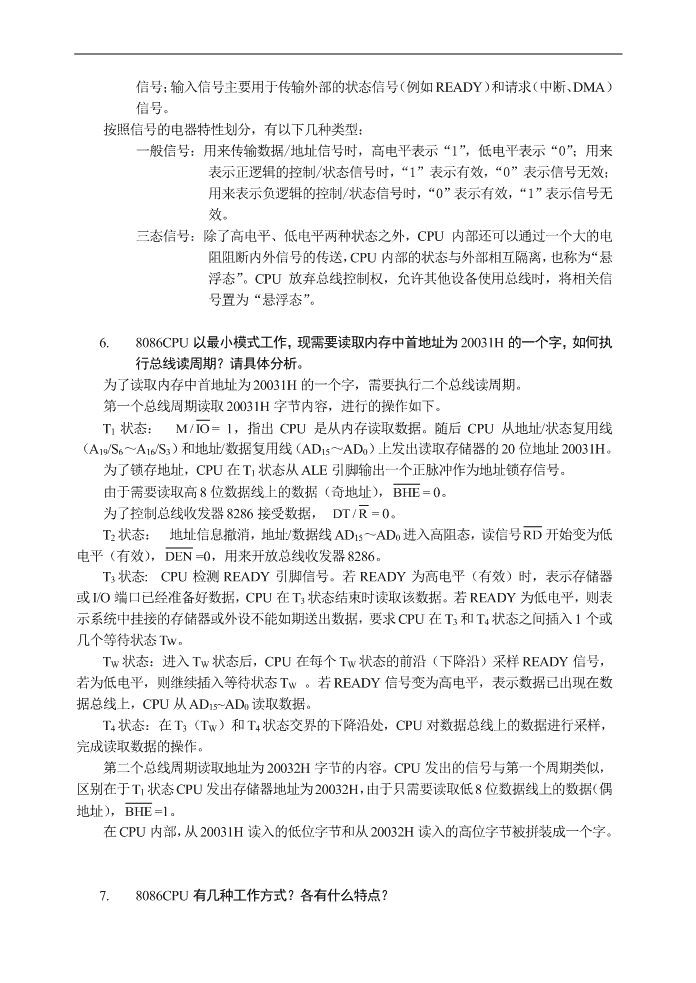

6.DRAM为什么需要定时刷新?DRAM靠MOS管极间电容存储电荷的有无决定所存信息是0还是1,由于漏电流的存在,它存储的信息不能长时间保存,需要定时重新写入,称为“刷新”。7.74LS138译码器的接线如图2.28所示,写出Y0、Y2、Y4、Y6所决定的内存地址范围。从图看出,该存储系统的片内地址线有13根(A12-A0),是一个由8KB存储芯片组成的存储系统,A17地址线不确定。它的地址分布为:00?0,CBA?,????,????,????其中,CBA作为译码输入,与输出选择有关;“?”表示可以为“0”,也可以为“1”。于是:Y0对应的内存地址范围是:00000H—01FFFH;或20000H—21FFFH。图2-28译码电路电路Y2对应的内存地址范围是:04000H—05FFFH;或24000H—25FFFH。Y4对应的内存地址范围是:08000H—09FFFH;或28000H—29FFFH。Y6对应的内存地址范围是:0C000H—0DFFFH;或2C000H—2DFFFH。8.叙述EPROM的编程过程,并说明EPROM和EEPROM的不同点。EPROM的编程过程标准编程方式:Vpp上加编程电压,地址线、数据线上给出要编程单元的地址及其数据,并使CE=0、OE=1。上述信号稳定后,在PRG端加上宽度为50±5ms的负脉冲,就可将一个字节的数据写入相应的地址单元中。不断重复这个过程,将数据逐一写入。快速编程方式:使用100µs的编程脉冲依次写完所有要编程的单元,然后从头开始校验每个写入的字节。若写得不正确,则重写这个单元。写完后再校验,不正确还可再写,直到全部正确。EPROM和EEPROM的不同点:EPROM芯片用紫外线光照射擦除芯片的内容,擦除时需要把芯片从电路板上拔下,擦

除操作对整个芯片进行。EPROM芯片编程需要外加“高电压”,所以需要专用的“编程器”才能实现。EPROM的编程一般情况下对整个芯片进行。EEPROM芯片的擦除用电信号实现,无需把芯片从电路板上拔下,可以进行“在系统编程”。EEPROM以字节为单位重写,EEPROM没有单独的擦除操作,写入就意味着擦除了原来的内容,所以使用比EPROM快速方便。相比较而言,EEPROM芯片的编程比较接近RAM的写入,它们之间的区别主要体现在速度上:RAM写入与读出的速度相近,不需要其他的联络信号;EEPROM的写入比起读出明显要慢,为了掌握写入时间,EEPROM通常设置了一根“状态”引脚,供联络使用。9.下列容量的ROM芯片除电源和地线,还有多少个输入引脚和输出引脚?写出信号名称。(1)64×4(2)512×8(3)128K×8(4)16K×8(5)1M×16根据存储容量计算公式可得以上各芯片的地址、数据引脚分别为:664×4:地址线k=log2(64)=log2(2)=6根,数据线=4根;9512×8:地址线k=log2(512)=log2(2)=9根,数据线=8根;17128k×8:地址线k=log2(128*1024)=log2(2)=17根,数据线=8根;1416k×8:地址线k=log2(16*1024)=log2(2)=14根,数据线=8根;201M×16:地址线k=log2(1024*1024)=log2(2)=20根,数据线=16根。此外,所有ROM芯片都需要一根片选信号引脚;对于PROM,EPROM通常还需要“输出允许”和“编程脉冲”输入引脚。EEPROM芯片除了有“片选”、“输出允许”和“写允许”外,通常还有表示“写入完成”的状态信号引脚。10.已知RAM芯片的容量为(1)16K×8(2)32K×8(3)64K×8(4)2K×8如果RAM的起始地址为3400H、则各RAM对应的末地址为多少?存储器的末地址=首地址+芯片内字节数(容量)-1上述各芯片对应RAM的末地址为:16K×8:末地址是3400H+4000H-1=73FFH32K×8:末地址是3400H+8000H-1=B3FFH64K×8:末地址是3400H+10000H-1=133FFH2K×8:末地址是3400H+800H-1=3BFFH11.如果存储器起始地址为1800H,末地址为1FFFH,求该存储器的容量。该存储器的容量为:(1FFFH-1800H+1)×8=800H×8,该存储器有2048×8个位,也可以写作2KB。12.有一个存储体,其地址线15条,数据线8条,则1)该存储体能够存储多少个汉字?

2)如果该存储体由2K×4位的芯片组成,需要多少片?3)采用什么方法扩展?分析各位地址线的使用。15该存储体容量为2×8=32KB,存储一个汉字需要二个字节,因此,它能够存储16384(16K)个汉字。需要2K×4位的芯片32片,[(32K×8)/(2K×4)=32]。可采用字位全扩展方法,由2片4位的芯片组成1组8位的存储单元,16组扩展成32K的8位存储体。芯片直接使用的地址线(片内地址)11根(A0-A10),另外需要4根高位地址,连接到4-16译码器输入端,产生16个译码信号用作16个芯片组的片选信号。剩余的地址线用来确定该存储体的首地址。13.试说明FlashMemory芯片的特点及28F040的编程过程。FlashMemory也称为“闪速存储器”,有时直接称之为“Flash”。Flash既有ROM非易失性的特点,又能够在线擦除和重写,既可读又可写,同时有很高的存取速度,具有集成度高,价格低,耗电少等优点。目前存取速度已突破了30ns,掉电后信息可以保持10年。2Flash的编程方法与EPROM相同,28F040的编程写入过程采用字节编程方式。首先,向28F040状态寄存器写入命令10H,再在指定的地址单元写入相应数据。接着查询状态,判断这个字节是否写好,若写好则重复上面过程写入下一个字节,直到全部字节写入。28F040的编程速度很快,一个字节的写入时间仅为8.6µs。14.利用全地址译码将6264芯片接到8088系统总线上,地址范围为30000H~31FFFH,画出逻辑图。全地址译码可以保证存储器芯片上的每一个单元在整个内存空间中具有唯一的、独占的一个地址。参考教材相关内容,6264芯片有13根地址线,剩余的高位7根地址线通过译码组合确定该芯片的起始地址(30000H)。由30000H地址得出对应的地址线状态为:00110000000000000000可以看出A13~A19地址线为0011000,所以译码组合应逻辑为:CS1=A13·A14·A15·A·A·A18·A191617=(A13·A14·A15·A18·A19)·(A16·A17)=A13+A14+A15+A18+A19+A16·A17全地址译码连接图具体逻辑如右图所示。15.若用2164芯片构成容量为128KB的存储器,需多少片2164?至少需多少根地址线?其中多少根用于片内寻址?多少根用于片选译码?2164A是容量为64K×1位的动态随机存储器芯片,构成128KB的存储器需要2164A芯

片16片[128K×8/(64K×1)=16]。17由于地址空间为128K,需要的地址线总数为17根(2=128K)。其中,片内地址线1616根(2=64K),片选地址线1根(17-16=1,)。每8个2164芯片构成一组,进行位扩展,得到64KB存储器。两个这样的“组”进行地址扩展,构成128KB的存储器。16.某8088系统用2764ROM芯片和6264SRAM芯片构成16KB的内存。其中,RAM的地址范围为FC000H-FDFFFH,ROM的地址范围为FE000H-FFFFFH。试利用74LS138译码,画出存储器与CPU的连接图,并标出总线信号名称。2764和6264均为8KB的存储芯片,需要13根地址线(A0~A12)用于片内寻址。8088系统的其他地址线(A13~A19)用于产生片选信号。FC000H的地址线状态为:11111100000000000000FE000H的地址线状态为:11111110000000000000将A13~A15用作译码输入,其他地址(A16~A19=1111)用作译码控制,可以得到如下译码控制电路,连接如下图所示。17.存储周期指的是(A)。A.存储器进行连续读或写操作所允许的最短时间间隔B.存储器的读出周期C.存储器进行连续写操作所允许的最短时间间隔D.存储器的写入周期存储周期是指连续两次访问存储器之间所需的最小时间。存取时间是CPU访问一次存储器(写入和读出)所需的时间。存储周期等于存取时间加上存储器的恢复时间。所以应选择A。18.某一EPROM芯片,其容量为32K×8,除电源和地线外,最小的输入引脚和输出引脚分别为(C)。A.15和8;B.32和8;C.17和8;D.18和10;容量为32K×8的EPROM芯片,其数据线为8根,地址线为15根,片选线1根,读写

控制线1根。其中地址线、片选线、读写控制线均为EPROM的输入信号,共17根。数据线在正常工作状态下用于EPROM输出,计8根。所以应选择C。19.掩膜ROM在制造时通过光刻是否连接MOS管来确定0和1,如果对应的某存储单元位没有连接MOS管,则该位信息为(C)。A.不确定;B.0;C.1;D.可能为0,也可能为1;掩膜ROM芯片内每一个二进制位对应于一个MOS管,该位上存储的信息取决于这个MOS管的栅极是否被连接到字线上。栅极被连接,该单元被选中时,漏极与“地”相通,输出低电平,该位存储的信息就是0。栅极未连接时,尽管字线被选中,输出端与“地”仍然不能导通,输出高电平,对应的信息为1。所以应选择C。20.SRAM和DRAM存储原理不同,它们分别靠(A)来存储0和1的。A.双稳态触发器的两个稳态和极间是否有足够的电荷B.内部熔丝是否断开和双稳态触发器C.极间电荷和浮置栅是否积累足够的电荷D.极间是否有足够的电荷和双稳态触发器的两个稳态静态随机存储器(SRAM)的每一个位存储单元有一个双稳态触发器,由4个晶体管组成,它们的状态确定了该存储单元存储的1位二进制信息。而动态随机存储器(DRAM)一般采用单管电路组成,它由一个MOS管T1和一个电容C构成。写入时其信息通过位线(数据线)存人电容C中(写入“1”对电容充电,写入“0”则对电容放电);读出时存储在电容C上的电荷通过T1输出到位线上。所以应选择A。

习题三1.如果用24b储存一个无符号数,这个数的范围是什么?如果储存的是一个补码表示的有符号数,那么这个数的范围又是什么?答:如果用24b储存一个无符号数,这个数的范围应为:0~224-1如果用24b储存一个补码表示的有符号数,这个数的范围应为:-223~+223-12.用符号‚〉‛把下面的数按从大到小的顺序‚连接‛起来[X1]补=10110111[X2]原=10110111[X3]反=10110111[X4]补=10110110[X5]无符号数=10110111解:X1=-01001001B,X2=-0110111B,X3=-01001000B,X4=-01001010B,X5=+10110111B因此:X5>X2>X3>X1>X43.用8位补码完成下列运算,用二进制‚真值‛的格式给出运算结果,并指出运算后CF、OF、ZF、SF、PF标志位的状态。(1)127+126(2)126-127(3)-100-120(4)-100-(-120)解:(1)127+126[127]补=01111111,[126]补=01111110,[127+126]补=11111101,[127+126]=-00000011(溢出)COZSP=01010(2)126-127[126]补=01111110,[-127]补=10000001,[126-127]补=11111111,[126-127]=-0000001COZSP=10011(3)-100-120[-100]补=10011100,[-120]补=10001000,[-100-120]补=00100100,[-100-120]=+00100100(溢出)COZSP=01001(4)-100-(-120)[-100]补=10011100,[-120]补=10001000,[[-120]补]求补=01111000,[-100-(-120)]补=00010100,[-100-(-120)]=+00010100COZSP=000014.把二进制代码1001011101011000分别‚看作‛是:

(1)二进制无符号数(2)二进制补码(3)压缩BCD码(4)非压缩BCD码哪一种情况下它代表的‚值‛最大?答:看作二进制无符号数时,它代表的“值”最大。分析:看作二进制补码时,它代表一个负数,而其它的情况下,它均为正数。因此,看作二进制补码时,它代表的值最小。把这组代码用十六进制数字形式写出:9758对于无符号数,它的值等于十六进制的9758H;对于压缩BCD码,它的值等于十进制的9758,显然小于9758H;对于非压缩BCD码,它的值等于十进制的78,显然更小于9758H;因此,看作二进制无符号数时,它代表的“值”最大。5.某数据段内有如下数据定义:Xdb30,30H,‘ABC’,2-3,?,11001010Bdw0FFH,-2,‚CD‛Ydd20dup(15,3dup(?),0)Zdb3dup(?)WdwZ-X假设变量X的偏移地址为20H。(1)写出变量X各数据在内存中的具体位置和相关内存单元的值。(2)写出变量Y,Z的偏移地址。(3)写出变量W的值0020H1EHX答:(1)变量X各数据在内存中的具体位置和相关内存单元的30H41H值如右图。42H变量Y的偏移地址为002EH;43H变量Z的偏移地址为002EH+4×5×20=01BEH0FFH00H变量W的值等于变量Z和X偏移地址之差0CAH01BEH-0020H=019EH0FFH它等于变量X、Y所占用内存单元的字节数。00H0FEH0FFH44H6.下列指令的源操作数段基址在哪个段寄存器中?43H(1)MOVAX,[BP][SI](2)MOVAX,CS:8[DI]002EHY(3)MOVAX,2[EBP*1](4)MOVAX,FS:4[ESP](5)MOVAX,2[EBP][EAX](6)MOVAX,[ECX][EBP*4](7)MOCAX,[EDX][EBP](8)MOVAX,ES:10[EBP][EAX*2]答:各指令源操作数段基址使用的段寄存器如下:(1)SS(2)CS(3)SS(4)FS(5)SS(6)DS(7)DS(8)ES

7.判断下列指令是否正确。若不正确,指出错误原因(1)MOVAX,[EBX](2)MOVSI,DL(3)MOVEBP,[ESP][EAX*3](4)LEAAX,3006H(5)MOV[BP][DI],0(6)MOV[SI],[DI](7)MOVES,1000H(8)MOVAX,X+2(9)MOVAX,CX+2(10)MOV[EAX][EAX*2],AL答:(1)指令MOVAX,[EBX]是正确的。(2)指令MOVSI,DL是错误的,两个操作数类型不匹配。(3)指令MOVEBP,[ESP][EAX*3]是错误的,比例因子不能为3。(4)指令LEAAX,3006H是错误的,LEA指令的源操作数必须为内存操作数。(5)指令MOV[BP][DI],0是错误的,操作数类型无法确定。(6)指令MOV[SI],[DI]是错误的,不能同时出现两个内存操作数。(7)指令MOVES,1000H是错误的,装载段寄存器时,源操作数不能为立即数。(8)如果“X”是用常数表达式定义的符号(例如:XEQU5+6),或者是用“DW”定义的内存变量,指令MOVAX,X+2是正确的。否则这条指令是错误的。(9)指令MOVAX,CX+2是错误的,源操作数表达式CX+2不是一个可以直接计算的“常数表达式”。(10)指令MOV[EAX][EAX*2],AL是正确的。8.现有(DS)=2000H,(BX)=0100H,(SI)=0002H,(20100H)=12H,(20101H)=34H,(20102H)=56H,(20103H)=78H,(21200H)=2AH,(21201H)=4CH,(21202H)=0B7H,(21203H)=65H,说明下列指令执行后AX寄存器的内容。(1)MOVAX,1200H(2)MOVAX,BX(3)MOVAX,[1200H](4)MOVAX,[BX](5)MOVAX,1100H[BX](6)MOVAX,[BX][SI](7)MOVAX,1100H[BX][SI]答:(1)指令MOVAX,1200H执行后,(AX)=1200H(立即数操作数)。(2)指令MOVAX,BX执行后,(AX)=0100H(寄存器操作数)。(3)指令MOVAX,[1200H]执行后,(AX)=4C2AH(直接地址,EA=1200H)(4)指令MOVAX,[BX]执行后,(AX)=3412H(寄存器间接寻址,EA=0100H)(5)指令MOVAX,1100H[BX]执行后,(AX)=4C2AH(相对地址,EA=1200H)(6)指令MOVAX,[BX][SI]执行后,(AX)=7856H(基址变址寻址,EA=0102H)(7)指令MOVAX,1100H[BX][SI]执行后,(AX)=65B7H(相对基址变址寻址,EA=1202H)9.下面两条指令的功能有什么区别?

MOVAX,BXMOVAX,[BX]答:指令“MOVAX,BX”把BX寄存器的内容装入到AX中。指令“MOVAX,[BX]”把内存储器一个字的内容装入AX寄存器。该字的段基址在DS中,偏移地址在BX中。10.写出执行以下计算的指令序列,其中各变量均为16位有符号数。(1)Z←W+(Z-X)(2)Z←W-(X+6)-(R+9)(3)Z←(W*X)/(Y+6),R←余数(4)Z←(W-X)/(5*Y)*2解:(1)MOVAX,WMOVBX,ZSUBBX,XADDAX,BXMOVZ,AX(2)MOVAX,WMOVBX,XADDBX,6SUBAX,BXMOVBX,RADDBX,9SUBAX,BXMOVZ,AX(3)MOVAX,WIMULXMOVBX,YADDBX,9IDIVBXMOVZ,AXMOVR,DX(4)MOVAX,YMOVBX,5IMULBXMOVBX,AXMOVAX,WSUBAX,XMOVCX,2

IMULCXIDIVBXMOVZ,AX11.一个双字长有符号数存放在DX(高位)AX(低位)中,写出求该数相反数的指令序列。结果仍存入DX,AX寄存器解:NOTDX;首先将(DX,AX)取反NOTAXADDAX,1;最低位加1,注意:不能用INC指令ADCDX,0;把进位(如果有)传递到高位12.内存缓冲区BUFFER定义如下,按照要求,写出指令序列BUFFERDB20DUP(?)(1)将缓冲区全部置为0,并使执行时间最短(2)将缓冲区全部置为空格字符(ASCII代码20H),使用的指令条数最少(3)将缓冲区各字节依次设置为0,1,2,3,4,……,19(4)将缓冲区各字节依次设置为0,-1,-2,-3,-4,……,-19(5)将缓冲区各字节依次设置为30,29,28,27,……,11(6)将缓冲区各字节依次设置为0,2,4,6,8,……,38(7)将缓冲区各字节依次设置为0,1,2,3,0,1,2,3,……,3解:(1)XOREAX,EAXMOVDWORDPTR[BUFFER],EAXMOVDWORDPTR[BUFFER+4],EAXMOVDWORDPTR[BUFFER+8],EAXMOVDWORDPTR[BUFFER+12],EAXMOVDWORDPTR[BUFFER+16],EAX(2)MOVAL,20HMOVCX,20LEABX,BUFFERONE:MOV[BX],ALINCBXLOOPONE(3)XORBX,BXMOVCX,20ONE:MOVBUFFER[BX],BLINCBXLOOPONE(4)XORBX,BX

XORAL,ALMOVCX,20ONE:MOVBUFFER[BX],ALINCBXDECALLOOPONE(5)XORBX,BXMOVAL,30MOVCX,20ONE:MOVBUFFER[BX],ALINCBXDECALLOOPONE(6)XORBX,BXXORAL,ALMOVCX,20ONE:MOVBUFFER[BX],ALINCBXADDAL,2LOOPONE(7)XORBX,BXMOVCX,5ONE:MOVBUFFER[BX],0MOVBUFFER[BX+1],1MOVBUFFER[BX+2],2MOVBUFFER[BX+3],3ADDBX,4LOOPONE13.编写循环结构程序,进行下列计算,结果存入RESULT内存单元(1)1+2+3+4+5+6+……+100(2)1+3+5+7+9+11+……+99(3)2+4+6+8+10+……+100(4)1+4+7+10+13+……+100(5)11+22+33+44+……+99解:(1)CODESEGMENTASSUMECS:CODE

RESULTDW?START:XORAX,AXMOVCX,100AGAIN:ADDAX,CXLOOPAGAINMOVRESULT,AXMOVAX,4C00HINT21HCODEENDSENDSTART(2)CODESEGMENTASSUMECS:CODERESULTDW?START:XORAX,AXMOVCX,50MOVBX,1AGAIN:ADDAX,BXADDBX,2LOOPAGAINMOVRESULT,AXMOVAX,4C00HINT21HCODEENDSENDSTART(3)CODESEGMENTASSUMECS:CODERESULTDW?START:XORAX,AXMOVCX,50MOVBX,2AGAIN:ADDAX,BXADDBX,2LOOPAGAINMOVRESULT,AXMOVAX,4C00H

INT21HCODEENDSENDSTART(4)CODESEGMENTASSUMECS:CODERESULTDW?START:XORAX,AXMOVCX,34MOVBX,1AGAIN:ADDAX,BXADDBX,3LOOPAGAINMOVRESULT,AXMOVAX,4C00HINT21HCODEENDSENDSTART(5)CODESEGMENTASSUMECS:CODERESULTDW?START:XORAX,AXMOVCX,9MOVBX,11AGAIN:ADDAX,BXADDBX,11LOOPAGAINMOVRESULT,AXMOVAX,4C00HINT21HCODEENDSENDSTART14.已知ARRAY是5行5列的有符号字数组,编写程序,进行下列计算(假设和仍然为16b,不会产生溢出)(1)求该数组第4列所有元素之和(列号从0开始)

(2)求该数组第3行所有元素之和(行号从0开始)(3)求该数组正对角线上所有元素之和(4)求该数组反对角线上所有元素之和解:假设数据段已定义如下:DATASEGMENTARRAYDW1,6,9,23,12;定义数组ARRAYDW54,23,15,-92,37;每一行5个数据DW-99,231,76,81,90;共5行DW33,67,81,-99,0;共计25个数据DW123,-52,77,-180,89SUMDW?;SUM存放结果DATAENDS(1)CODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAX,0;累加器在循环之前清零MOVCX,5;计数器置初值MOVSI,4*2;第1行第4列元素在数组内的位移NEXT:ADDAX,ARRAY[SI]ADDSI,5*2;SI指向下一行第4列元素LOOPNEXTMOVSUM,AXMOVAX,4C00HINT21HCODEENDSENDSTART(2)CODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAX,0;累加器在循环之前清零MOVCX,5;计数器置初值MOVSI,3*5*2;第3行第0列元素在数组内的位移NEXT:ADDAX,ARRAY[SI]ADDSI,2;SI指向本行下一列元素LOOPNEXT

MOVSUM,AXMOVAX,4C00HINT21HCODEENDSENDSTART(3)CODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAX,0;累加器在循环之前清零MOVCX,5;计数器置初值MOVSI,0;第0行第0列元素在数组内的位移NEXT:ADDAX,ARRAY[SI]ADDSI,5*2+2;SI指向正对角线上下一个元素LOOPNEXTMOVSUM,AXMOVAX,4C00HINT21HCODEENDSENDSTART(4)CODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAX,0;累加器在循环之前清零MOVCX,5;计数器置初值MOVSI,4*2;第0行第4列元素在数组内的位移NEXT:ADDAX,ARRAY[SI]ADDSI,(5-1)*2;SI指向反对角线上下一个元素LOOPNEXTMOVSUM,AXMOVAX,4C00HINT21HCODEENDSENDSTART15.变量X,Y,Z均为一字节压缩BCD码表示的十进制数,写出指令序列,求它们的和(用

2字节压缩BCD码表示)。解:XORAX,AX;清AX,用于存放2字节结果MOVAL,XADDAL,Y;完成X+YDAA;压缩BCD码加法调整ADCAH,0;把可能的进位收集到AH中;AH中最大的可能值为2,因此不需要BCD加法调整ADDAL,Z;完成X+Y+ZDAA;压缩BCD码加法调整ADCAH,0;把可能的进位收集到AH中;计算完成,结果(2字节压缩BCD码)在AX中16.设(BX)=0E3H,变量VALUE中存放内容为79H,指出下列指令单独执行后的结果。(1)XORBX,VALUE(2)ANDBX,VALUE(3)ORBX,VALUE(4)XORBX,0FFH(5)ANDBX,BX(6)ANDBX,0答:(1)指令“XORBX,VALUE”执行后,(BX)=009AH(2)指令“ANDBX,VALUE”执行后,(BX)=0061H(3)指令“ORBX,VALUE”执行后,(BX)=00FBH(4)指令“XORBX,0FFH”执行后,(BX)=001CH(5)指令“ANDBX,BX”执行后,(BX)=00E3H(6)指令“ANDBX,0”执行后,(BX)=0000H17.编写程序,从键盘上输入20个十进制数字,求这些数字的和,向显示器输出。INCLUDEYLIB.HDATASEGEMNTMESS1DB0DH,0AH,„Input20decimaldigitsplease:$‟MESS2DB0DH,0AH,„Theirsumis:$‟DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AX

LEADX,MESS1MOVAH,09HINT21H;输出提示信息XORBX,BX;BX用作累加器,清零MOVCX,20;循环计数器置初值AGAIN:MOVAH,01HINT21H;输入一个数字(在AL中)ANDAL,0FH;转换成二进制数ADDBL,AL;累加ADCBH,0LOOPAGAINLEADX,MESS2MOVAX,BXCALLWRITEDEC;输出20个数字的和CALLCRLFMOVAX,4C00HINT21HCODEENDSENDSTART18.阅读以下程序,指出它的功能。MOVCL,04SHLDX,CLMOVBL,AHSHLAX,CLSHRBL,CLORDL,BL答:把32位二进制代码(DX,AX)联合左移4位。19.已知(DX)=0B9H,(CL)=3,(CF)=1,确定下列指令单独执行以后DX寄存器的值。(1)SHRDX,1(2)SARDX,CL(3)RORDX,CL(4)ROLDX,CL(5)SALDH,1(6)RCLDX,CL答:

(1)指令“SHRDX,1”执行之后,(DX)=005CH(2)指令“SARDX,CL”执行之后,(DX)=0017H(3)指令“RORDX,CL”执行之后,(DX)=2017H(4)指令“ROLDX,CL”执行之后,(DX)=05C8H(5)指令“SALDH,1”执行之后,(DX)=00B9H(6)指令“RCLDX,CL”执行之后,(DX)=05CCH20.写程序,从键盘上输入一个0~65535之间的十进制无符号数,然后用二进制格式输出这个值。例如,键盘输入‚35‛,显示器输出‚0000000000100011‛。答:INCLUDEYLIB.HDATASEGEMNTMESS1DB0DH,0AH,„Inputaunsigneddecimalintegernumberplease:$‟MESS2DB0DH,0AH,„Thenumberinbinaryis:$‟DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEADX,MESS1CALLREADDEC;输入一个无符号整数MOVBX,AX;转存入BXLEADX,MESS2MOVAH,09HINT21H;输出提示信息MOVCX,16;循环计数器置初值AGAIN:SHLBX,1;向左外移一位,进入CFMOVDL,30HADCDL,0;形成一位二进制数字的ASCII代码MOVAH,2INT21H;输出一个二进制数字LOOPAGAIN;循环16次CALLCRLFMOVAX,4C00HINT21HCODEENDSENDSTART21.无符号数变量X用DD定义,编写程序,用十六进制格式输出变量X的值。

答:DATASEGEMNTXDD36895471;一个32B长整数MESSDB0DH,0AH,„TheXinhexdecimalis:$‟HEXTABDB„0123456789ABCDEF‟DATAENDSCODESEGMENTUSE16ASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEADX,MESSMOVAH,09HINT21H;输出前导信息MOVSI,wordptrX+2;将X高16位存入SIMOVCX,4;循环计数器置初值LEABX,HEXTAB;换码表首地址装入BXAGAIN1:ROLSI,4;把最高4位移到最低4位上MOVAX,SI;低8位转入ALANDAX,000FH;清除高4位XLAT;转换成十六进制数字的ASCII代码MOVDL,ALMOVAH,2INT21H;输出一个十六进制数字LOOPAGAIN1;循环8次MOVSI,wordptrX;将X低16位存入SIMOVCX,4;循环计数器置初值AGAIN2:ROLSI,4;把最高4位移到最低4位上MOVAX,SI;低8位转入ALANDAX,000FH;清除高4位XLAT;转换成十六进制数字的ASCII代码MOVDL,ALMOVAH,2INT21H;输出一个十六进制数字LOOPAGAIN2;循环8次MOVAX,4C00HINT21HCODEENDSENDSTART

22.编写指令序列,把AX中的16b二进制分为4组,每组4b,分别置入AL,BL,CL,DL中。答:MOVDX,AX;最低4位直接进入DXMOVCX,4ROLAX,CL;最高4位移入最低4位PUSHAX;压入堆栈保存(准备送入AL)ROLAX,CL;次高4位移入最低4位MOVBX,AX;送入BLROLAX,CL;第3组4位移入最低4位MOVCX,AX;送入CLPOPAX;从堆栈中弹出原最高4位ANDAX,000FH;清除高12位ANDBX,000FH;清除高12位ANDCX,000FH;清除高12位ANDDX,000FH;清除高12位

习题四1.什么是‚三种基本结构‛?解释‚基本‛两个字在其中的含义。答:三种基本结构指:顺序结构,选择结构、循环结构。使用这3种结构,可以编制出任何所需要的程序,因此冠以“基本”结构。2.什么叫做‚控制转移指令‛?它和数据传送、运算指令有什么区别?它是怎样实现它的功能的?答:控制转移指令是可以改变指令执行顺序的指令。数据传送、运算指令总是顺序执行的,而控制转移指令通过改变IP和/或CS寄存器的值,改变了程序指令的执行顺序。3.指令‚JMPDI‛和‚JMPWORDPTR[DI]‛作用有什么不同?请说明。答:上述两条指令都是段内近转移指令,但是偏移地址的来源不同。指令“JMPDI”执行时,新的偏移地址在DI寄存器内,“JMPWORDPTR[DI]”时,目的偏移地址在存储单元中,该存储单元的地址在DS:DI中。4.已知(AX)=836BH,X分别取下列值,执行‚CMPAX,X‛后,标志位ZF、CF、OF、SF各是什么?(1)X=3000H(2)X=8000H(3)X=7FFFFH(4)X=0FFFFH(5)X=0答:上述指令执行后,标志位ZF、CF、OF、SF的状态分别是:(1)ZCOS=0010(2)ZCOS=0000(3)ZCOS=0010(4)ZCOS=0101(5)ZCOS=00015.已知(AX)=836BH,X分别取下列值,执行‚TESTAX,X‛后,标志位ZF、CF、OF、SF各是什么?(1)X=0001H(2)X=8000H(3)X=0007H(4)X=0FFFFH(5)X=0答:上述指令执行后,标志位ZF、CF、OF、SF的状态分别是:(1)ZCOS=0000(2)ZCOS=0001(3)ZCOS=0000(4)ZCOS=0001(5)ZCOS=10006.测试名为X的一个字节,如果X的第1,3位均为1,转移到L1,如果只有一位为1,转移到L2,如果两位全为0,转移到L3。写出对应的指令序列。答:MOVAL,XANDAL,00001010BJZL3CMPAL,00001010BJEL1JMPL2

7.假设X和X+2字单元存放有双精度数P,Y和Y+2字单元存放有双精度数Q,下面程序完成了什么工作?MOVDX,X+2MOVAX,X;双精度数P送入DX,AXADDAX,XADCDX,X+2;计算2*P送入DX,AXCMPDX,Y+2;2P与Q的高位比较JLL2;2PQ,转L1(Z=1)CMPAX,Y;如果高位相等,则比较低位JBEL2;2P的低位小于等于Q的低位,转L2(Z=2)L1:MOVZ,1JMPSHORTEXITL2:MOVZ,2EXIT:……答:程序根据2P与Q的大小,确定Z的值。如果2P≤Q,则Z=2如果2P>Q,则Z=1请参阅程序注解8.编写指令序列,将AX和BX中较大的绝对值存入AX,较小的绝对值存入BX。答:ANDAX,AXJGESKIP1NEGAXSKIP1:ANDBX,BXJGESKIP2NEGBXSKIP2:CMPAX,BXJGESKIP3XCHGAX,BXSKIP3:……9.编写指令序列,比较AX、BX中的数的绝对值,绝对值较大的数存入AX,绝对值较小的数存入BX。答:PUSHAXPUSHBXANDAX,AXJGESKIP1NEGAX

SKIP1:ANDBX,BXJGESKIP2NEGBXSKIP2:CMPAX,BXPOPBXPOPAXJGESKIP3XCHGAX,BXSKIP3:……10.编写指令序列,如果AL寄存器存放的是小写字母,把它转换成大写字母,否则不改变AL内容。答:CMPAL,„a‟JBDONECMPAL,„z‟JADONESUBAL,„a‟-„A‟DONE:……X3X211.计算分段函数:Y5X62X32X3X的值从键盘输入,Y的值送显示器输出。答:INCLUDEYLIB.HDATASEGEMNTMESS1DB0DH,0AH,„InputvalueofXplease:$‟MESS2DB0DH,0AH,„Y=:$‟DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEADX,MESS1CALLREADINT;输入X的值CMPAX,-2JGEL2L1:SUBAX,3;AX←X-3

JMPDONEL2:CMPAX,3JGL3MOVBX,AXADDAX,AX;AX←2XADDAX,AX;AX←4XADDAX,BX;AX←5XADDAX,6;AX←5X+6JMPDONEL3:MOVAX,2;AX←2DONE:LEADX,MESS2CALLWRITEINT;输出Y的值CALLCRLFMOVAX,4C00HINT21HCODEENDSENDSTARTAB(A0)(B0)12.计算分段函数:Y2(A0)(B0)AB(A0)(B0)A,B的值从键盘输入,Y的值送显示器输出(∧表示‚并且‛,∨表示‚或者‛)。答:INCLUDEYLIB.HDATASEGEMNTMESS1DB0DH,0AH,„InputthevalueofAplease:$‟MESS2DB0DH,0AH,„InputthevalueofBplease:$‟MESS3DB0DH,0AH,„Y=:$‟ADW?BDW?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEADX,MESS1CALLREADINT;输入A

MOVA,AXLEADX,MESS2CALLREADINT;输入BMOVB,AXANDAX,AXJLL1;B<0,转L1CMPA,0JLL1;A<0,转L1JNZSKIP1CMPB,0JZL2;A=0&&B=0,转L2JMPEXIT;A=0&&B≠0,无定义,转EXITSKIP1:CMPB,0JLEEXIT;A≠0&&B=0,无定义,转EXITL3:MOVAX,ASUBAX,BJMPDISPL2:MOVAX,2JMPDISPL1:MOVAX,AADDAX,BDISP:LEADX,MESS2CALLWRITEINT;输出Y的值CALLCRLFEXIT:MOVAX,4C00HINT21HCODEENDSENDSTART说明:如果把A、B看作是平面直角坐标的两根轴,那么这个函数在A,B的正轴上无定义。无法计算,也无法输出结果。13.编写程序,求10元素字数组LIST中绝对值最小的数,存入MIN单元。答:DATASEGEMNTLISTDW-56,+12,88,-126,-5,16,32,-99,72,-18MINDW?MINABSDW?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATA

START:MOVAX,DATAMOVDS,AXMOVAX,LISTMOVMIN,AX;将数组第一个元素假设为绝对值最小的数MOVMINABS,32767;最小的绝对值假设为32767LEASI,LISTMOVCX,10AGAIN:MOVAX,[SI]CMPAX,0JGESKIP1NEGAX;求绝对值SKIP1:CMPAX,MINABS;绝对值与假设的最小绝对值比较JGESKIP2;假设的绝对值较小,跳过MOVMINABS,AX;保存新的最小绝对值MOVAX,[SI];取出新的绝对值最小的数MOVMIN,AX;保留新的绝对值最小的数SKIP2:ADDSI,2LOOPAGAINMOVAX,4C00HINT21HCODEENDSENDSTART说明:一定要预设最小的绝对值和绝对值最小的数,而且这个绝对值最小的数必须来自LIST数组。14.编写程序,求20元素无符号字数组ARRAY中最小的奇数,存入ODD单元,如果不存在奇数,将ODD单元清零。答:DATASEGEMNTARRAYDW56,12,88,126,5,16,32,99,72,18DW116,34,92,32,156,42,816,16,15,218ODDDW?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVBX,0

MOVODD,65535;将65535假设为最小的奇数LEASI,ARRAYMOVCX,20AGAIN:MOVAX,[SI]TESTAX,1;测试是否为奇数JZSKIP;不是奇数跳过INCBX;记录奇数个数CMPAX,ODD;奇数与预设的最小奇数比较JGESKIP;大于预设奇数,跳过MOVODD,AX;小于预设奇数,保留SKIP:ADDSI,2LOOPAGAINCMPBX,0;判有无出现过奇数JNZDONEMOVODD,0;未出现过,把ODD单元清零DONE:MOVAX,4C00HINT21HCODEENDSENDSTART15.一个有符号字数组以0为结束标志,求这个数组的:最大值、最小值、平均值。答:DATASEGEMNTLISTDW-56,+12,88,-126,-5,16,32,-99,72,-18,0MINDW?MAXDW?AVGDW?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVMIN,32767;将32767假设为最小的数MOVMAX,-32768;将-32768假设为最大的数MOVAVG,0;AVG用作累加器,清零LEASI,LISTMOVCX,0AGAIN:MOVAX,[SI]CMPAX,0

JZDONE;找到零元素,转DONE结束处理INCCX;记录非零元素个数ADDAVG,AX;累加CMPAX,MINJGESKIP1MOVMIN.AX;比预设最小值还小,保留SKIP1:CMPAX,MAXJLESKIP2MOVMAX,AX;比预设最大值还大,保留SKIP2:ADDSI,2JMPAGAINDONE:JCXZNULL;元素个数为零,转NULL处理MOVAX,AVGCWDIDIVCXMOVAVG,AX;计算平均值JMPEXITNULL:MOVMIN,0;元素个数为0,将“最大值”、“最小值”MOVMAX,0;“平均值”清零MOVAVG,0EXIT:MOVAX,4C00HINT21HCODEENDSENDSTART16.数组SCORE中存有一个班级40名学生的英语课程成绩。按照0~59,60~74,75~84,85~100统计各分数段人数,存入N0,N1,N2,N3变量内。答:DATASEGEMNTSCOREDW40DUP(?);运行前置入具体数据N0DW?N1DW?N2DW?N3DW?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AX

MOVN0,0;各计数器清零MOVN1,0MOVN2,0MOVN3,0LEASI,SCOREMOVCX,40AGAIN:MOVAX,[SI]CMPAX,59;分段测试JAL1L0:INCN0JMPNEXTL1:CMPAX,74JAL2INCN1JMPNEXTL2:CMPAX,84JAL3INCN2JMPNEXTL3:CMPAX,100JANEXTINCN3NEXT:ADDSI,2LOOPAGAINEXIT:MOVAX,4C00HINT21HCODEENDSENDSTART17.STRING是一个16个字符组成的字符串,RULE是一个字整数。编写程序,测试STRING中的每一个字符,如果该字符为数字字符,把RULE中对应位置1,否则置0。答:DATASEGEMNTSTRINGDB16DUP(?);运行前置入具体字符RULEDW?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATA

MOVDS,AXMOVRULE,0;RULE置为初始状态LEASI,STRINGMOVCX,16AGAIN:SHLRULE,1;右侧空出一位MOVAL,[SI]CMPAL,„0‟;测试是否数字JBNEXTCMPAL,„9‟JANEXTORRULE,1;将RULE对应位置1NEXT:INCSILOOPAGAINEXIT:MOVAX,4C00HINT21HCODEENDSENDSTART18.编写程序,从键盘上输入一个无符号字整数,用‚四进制‛格式输出它的值(也就是,每2位二进制看作一位四进制数,使用数字0~3)。答:INCLUDEYLIB.HDATASEGEMNTMESS1DB0DH,0AH,„Inputanumberplease:$‟MESS2DB0DH,0AH,„Thenumberinquardri_systemis:$‟DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEADX,MESS1CALLREADDEC;输入一个无符号整数MOVBX,AX;转存到BXLEADX,MESS2MOVAH,9INT21H;输出前导信息MOVCX,8ONE:ROLBX,1ROLBX,1;最高2位移到最低位

MOVDL,BL;转存到DLANDDL,00000011B;保留最低2位ORDL,30H;转换成ASCII代码MOVAH,2INT21H;输出LOOPONECALLCRLFMOVAX,4C00HINT21HCODEENDSENDSTART19.编写程序,把一个30个元素的有符号字数组ARRAY按照各元素的正负分别送入数组P和M,正数和零元素送P数组,负数送M数组。答:DATASEGEMNTARRAYDW30DUP(?);汇编之前置入数据PDW30DUP(?)MDW30DUP(?)DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEABX,ARRAY;ARRAY数组指针MOVSI,0;P数组指针MOVDI,0;M数组指针MOVCX,30ONE:MOVAX,[BX];从ARRAY数组取出一个数据ANDAX,ALJGEPLUS;正数、零转PLUSMINUS:MOVM[DI],AX;负数存入M数组ADDDI,2JMPNEXTPLUS:MOVP[SI],AX;正数、零存入P数组ADDSI,2NEXT:ADDBX,2LOOPONEMOVAX,4C00H

INT21HCODEENDSENDSTART20.缓冲区BUFFER中存放有字符串,以0为结束标志。编写程序,把字符串中的大写字母转换成小写字母。答:DATASEGEMNTBUFFERDB„AStringforTest.‟,0DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEABX,BUFFER;BUFFER缓冲区指针ONE:MOVAL,[BX];从缓冲区取出一个字符ANDAL,ALJZQUIT;为零,处理完成CMPAL,„A‟JBNEXTCMPAL,„Z‟JANEXTADDAL,„a‟-„A‟MOV[BX],ALNEXT:INCBXJMPONEQUIT:MOVAX,4C00HINT21HCODEENDSENDSTART21.编写程序,从键盘上输入无符号字整数X,Y的值,进行X+Y的运算,然后按以下格式显示运算结果和运算后对应标志位的状态。SUM=XXXXZF=Y,OF=Y,SF=Y,CF=Y(其中X为十进制数字,Y为0或1)答:INCLUDEYLIB.HCODESEGMENTASSUMECS:CODE

MESS1DB0DH,0AH,„Inputaunsignedintegerplease:$‟MESS2DB0DH,0AH,„SUM=$‟MESS3DB0DH,0AH,„ZF=‟ZFDB?DB„,OF=‟OFDB?DB„,SF=‟SFDB?DB„,CF=‟CFDB?DB0DH,0AH,„$‟START:PUSHCSPOPDSLEADX,MESS1CALLREADDECMOVCX,AX;输入XLEADX,MESS1CALLREADDEC;输入YADDAX,CX;求和PUSHF;保留标志位状态LEADX,MESS2CALLWRITEDEC;输出两个数的和POPBX;标志寄存器内容转存入BXMOVAL,„0‟TESTBX,1000000B;测试ZFJZSKP1INCALSKIP1:MOVZF,ALMOVAL,„0‟TESTBX,100000000000B;测试OFJZSKP2INCALSKIP2:MOVOF,ALMOVAL,„0‟TESTBX,10000000B;测试SFJZSKP3INCALSKIP3:MOVSF,AL

MOVAL,„0‟TESTBX,1;测试CFJZSKP4INCALSKIP4:MOVCF,ALLEADX,MESS3MOVAH,9INT21H;输出标志位状态MOVAX,4C00HINT21HCODEENDSENDSTART22.编写程序,从键盘上输入一个字符串,统计其中数字字符,小写字母,大写字母,空格的个数并显示。答:INCLUDEYLIB.HCODESEGMENTASSUMECS:CODEMESS1DB0DH,0AH,„Inputastringplease:$‟BUFFERDB81,?,81DUP(?)MESS2DB0DH,0AH,„Digits:$‟MESS3DB0DH,0AH,„Uppercasealphabet:$‟MESS4DB0DH,0AH,„Lowercasealphabet:$‟MESS5DB0DH,0AH,„Space:$‟START:PUSHCSPOPDSLEADX,MESS1MOVAH,09HINT21H;输出提示信息LEADX,BUFFERMOVAH,0AHINT21H;输入字符串XORDX,DX;各计数器清零XORBX,BXMOVCL,BUFFER+1MOVCH,0;字符个数送CXLEASI,BUFFER+2;设置字符指针

ONE:MOVAL,[SI];取出一个字符CMPAL,„„JNEL2L1:INCDL;空格字符计数JMPNEXTL2:CMPAL,„0‟JBNEXTCMPAL,„9‟JAL4L3:INCDH;数字字符计数JMPNEXTL4:CMPAL,„A‟JBNEXTCMPAL,„Z‟JAL6L5:INCBH;大写字符计数JMPNEXTL6:CMPAL,„a‟JBNEXTCMPAL,„z‟JANEXTINCBL;小写字母计数NEXT:INCSILOOPONE;循环控制PUSHDXMOVAL,DHLEADX,MESS2MOVAH,0CALLWRITEDEC;输出数字字符个数LEADX,MESS4MOVAL,BLMOVAH,0CALLWRITEDEC;输出小写字母个数LEADX,MESS3MOVAL,BHMOVAH,0CALLWRITEDEC;输出大写字母个数POPDXMOVAL,DL

MOVAH,0LEADX,MESS5CALLWRITEDEC;输出空格个数MOVAX,4C00HINT21HCODEENDSENDSTART23.编写程序,读入20个数据,统计每个相同数据出现的次数。答:INCLUDEYLIB.HDATASEGEMNTNUMBERDW20DUP(?)TIMESDW20DUP(?)MESSDB0DH,0AH,„InputanumberofNO.$‟DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEASI,NUMBERMOVCX,20MOVBX,1INPUT:LEADX,MESSMOVAX,BXCALLWRITEDEC;输出提示信息和序号MOVDX,-1CALLREADDEC;输入一项数据MOV[SI],AL;保存成绩INCBXADDSI,2LOOPINPUTLEABX,TIMESMOVCX,20INIT:MOVBYTEPTR[BX],-1;将“出现次数”初始值设为-1ADDBX,2LOOPINIT

MOVDI,0;DI为被统计数据指针MOVCX,20STAT0:PUSHCXMOVCX,20MOVSI,0;SI为其它数据的指针MOVAL,NUMBER[DI];取出被统计数据STAT1:CMPAL,NUMBER[SI];与其他数据相比较JNESKIPINCTIMES[DI];出现相同数据,次数加1SKIP:ADDSI,2LOOPSTAT1;比较下一个数据POPCXADDDI,2LOOPSTAT0MOVAX,4C00HINT21HCODEENDSENDSTART24.编写程序,打印九九乘法表。答:INCLUDEYLIB.HCODESEGMENTASSUMECS:CODESPACEDB„$‟;乘积不足两位时补一个空格START:CALLCRLFMOVSI,1;SI为被乘数MOVCX,9LOOP0:PUSHCXMOVCX,9MOVDI,1;DI为乘数LOOP1:MOVAX,SIMULDIMOVDX,-1CMPAX,10JAESKIP

LEADX,SPACE;乘积不足两位时补一个空格SKIP:CALLWRITEDEC;输出乘积INCDILOOPLOOP1CALLCRLF;结束一行INCSIPOPCXLOOPLOOP0MOVAX,4C00HINT21HCODEENDSENDSTART子程序WRITEDEC输出时,数据前后各留出一个空格。程序中对一位数的乘积补上一个空格,这样每个数据共占用4个字符位置,使输出对齐。25.编写程序,显示1000以内的所有素数。答:INCLUDEYLIB.HCODESEGMENTASSUMECS:CODESTART:CALLCRLFMOVSI,2;SI为被测试的1000以内的整数MOVCX,0;CX记录一行上已输出数据个数;每行输出10个素数ONE:MOVDI,SISHRDI,1;计算测试范围MOVBX,2;第一个测试数据TST:CMPBX,DI;测试完成?JAOK;测试完成,是素数,转OKMOVAX,SICWDDIVBX;除法测试CMPDX,0JZNEXT;整除,本数据非素数,转NEXTINCBX;形成下一个测试数据JMPTST;继续测试OK:INCCX;统计本行输出数据个数CMPCX,10

JLEOUTPUT;本行数据未满10个,直接输出XORCX,CX;本行数据已满10个,清计数器CALLCRLF;输出回车换行OUTPUT:MOVDX,-1MOVAX,SICALLWRITEDEC;输出一个素数NEXT:INCSI;产生下一个被测试数据CMPSI,1000JBONE;未完成,继续CALLCRLF;结束一行MOVAX,4C00HINT21HCODEENDSENDSTART26.编写程序,输入N,计算:S=1*2+2*3+……+(N-1)*N答:INCLUDEYLIB.HCODESEGMENTASSUMECS:CODEMESS1DB0DH,0AH,„InputNplease:$‟MESS2DB0DH,0AH,„S=$‟START:PUSHCSPOPDSLEADX,MESS1CALLREADDEC;输入NMOVCX,AXXORBX,BX;BX用作累加器ONE:MOVAX,CXMOVSI,AXDECSIMULSI;计算J*(J-1)ADDBX,AX;累加LOOPONELEADX,MESS2MOVAX,BXCALLWRITEDEC;输出结果CALLCRLFMOVAX,4C00H

INT21HCODEENDSENDSTART27.编写程序,输入N,输出如下矩阵(设N=5)1111122221333214432154321答:设I为行(1~5),J为列(1~5),则(I,J)位置上的数据为:I>(6-J)?I:6-J。INCLUDEYLIB.HCODESEGMENTASSUMECS:CODESTART:CALLCRLFMOVSI,1;SI为行号ROW:MOVCX,5;CX为6-列号COL:CMPSI,CX;判断当前位置JBUPDOWN:MOVAX,CX;下半三角,取6-列号JMPOUTPUTUP:MOVAX,SI;上半三角,取行号OUTPUT:MOVDX,-1CALLWRITEDEC;输出一个数据LOOPCOLCALLCRLF;结束本行INCSI;修改行号CMPSI,5JBEROW;未满5行,继续MOVAX,4C00HINT21HCODEENDSENDSTART28据下面条件,画出每次调用子程序或返回时的堆栈状态。(1)主程序调用NEAR属性的SUB1子程序,返回的偏移地址为1200H.(2)进入SUB1后调用NEAR属性的SUB2子程序,返回的偏移地址为2200H.

(3)进入SUB2后调用FAR属性的SUB3子程序,返回的段基址为4000H,偏移地址为0200H。(4)从SUB3返回SUB2后。(5)从SUB2返回SUB1后。(6)从SUB1返回主程序后。解:SP0200HSP2240SP1200H00H00H122200H00HCALLSUB112CALLSUB200HCALLFARPTRSUB302020200H00H00H40404000H00H00HSP22222200H00H00H12SP121200H00H00H29编写几个简单的子程序。SP(1)显示一个字符的子程序。入口参数:从SUB3返回从SUB2返回DL=字符的SUB1ASCII码。从SUB1返回主(2)从键盘上读取一个字符的子程序。出口参数:读取字符的SUB2后。后程序后ASC码在CHAR中。(3)输出换行回车的子程序。无入口、出口参数。解:(1)SHOWPROCMOVAH,02HINT21HRETSHOWENDP(2)READKEYPROCMOVAH,01HINT21HMOVCHAR,ALRET

READKEYENDP(3)CRLFPROCMOVAL,0AHMOVAH,02HINT21HMOVAL,0DHINT21HRETCRLFENDP30阅读下面的子程序,叙述它完成的功能,它的入口参数和出口参数各是什么?CLSCREENPROCMOVAX,0600HMOVCX,0MOVDH,XMOVDL,YMOVBH,07HINT10HRETCLSCREENENDP解:屏幕窗口上卷,左上角为(0,0),右下角为(y,x),卷入行属性为黑底白字。31编写程序,键入一个以$为结束符的数字串,统计其中‚0‛~‚9‛各个数字出现的次数,分别存放到S0~S9这10个单元中去。解:.MODELSMALL.DATAS0DB0S1DB?S2DB0S3DB0S4DB0S5DB0S6DB0S7DB0S8DB0S9DB0KEYINDB100DUP(0).CODESTART:MOVAX,@DATA

MOVDS,AXMOVCX,0LEABX,KEYINNEXT:MOVAH,01HINT21HCMPAL,"$"JZCOUNTINCCXMOV[BX],ALINCBXJMPNEXTCOUNT:LEABX,KEYINCOUNT1:LEADI,S0MOVAL,[BX]SUBAL,30HMOVAH,0ADDDI,AXINCBYTEPTR[DI]INCBXLOOPCOUNT1MOVAX,4C00HINT21HENDSTART32编写求绝对值的子程序,利用它计算3个变量的绝对值之和。解:.MODELSMALL.DATAVALUEDW-5,5,-10SUMDW0.CODESTART:MOVAX,@DATAMOVDS,AXLEABX,VALUEMOVCX,3MOVSUM,0ONE:CALLABSADDSUM,AXADDBX,2LOOPONE

MOVAX,4C00HINT21H;子程序ABS;功能:求一个字整数的绝对值;入口:字整数的偏移地址在BX中;出口:该字整数的绝对值在AX中ABSPROCMOVSUM,0AGAIN:MOVAX,[BX]ANDAX,AXJGESKIPNEGAXSKIP:RETABSENDPENDSTART33子程序计算从2开始的N(N<50)个偶数之和(2+4+6+…),主程序从键盘输入整数N,调用子程序求出N个偶数之和,并显示结果。解:INCLUDEYLIB.H.MODELSMALL.DATASUMDW0PROMPT1DB0DH,0AH,"INPUTTHENUMBERN:$"PROMPT2DB0DH,0AH,"THESUMIS:$".CODESTART:MOVAX,@DATAMOVDS,AXLEADX,PROMPT1CALLREADDECCMPAX,0JZEXITMOVCX,AXCALLSUMMLEADX,PROMPT2CALLWRITEDECCALLCRLFEXIT:MOVAX,4C00HINT21H

SUMMPROCMOVAX,0NEXT:MOVBX,CXADDBX,BXADDAX,BXLOOPNEXTRETSUMMENDPENDSTART34从键盘输入一串字符,以$为结束符,存储在BUF中。子程序把字符串中的大写字母改成小写字母,最后由主程序把字符串送显示器输出。解:.MODELSMALL.DATABUFDB100DUP(?).CODESTART:MOVAX,@DATAMOVDS,AXLEABX,BUFCALLKEYINCALLCONVERTLEADX,BUFMOVAH,09HINT21HMOVAX,4C00HINT21HKEYINPROCPUSHBXMOVCX,0NEXT:MOVAH,01HINT21HMOV[BX],ALCMPAL,"$"JZEXITINCCXINCBXJMPNEXT

EXIT:POPBXRETKEYINENDPCONVERTPROCCONVERT1:MOVAL,[BX]CMPAL,"A"JBNEXT1CMPAL,"Z"JANEXT1ADDBYTEPTR[BX],20HNEXT1:INCBXLOOPCONVERT1RETCONVERTENDPENDSTART35从键盘输入一个字符串(长度<80),若该字符串不包括非数字字符,则显示‚YES‛,否显示‚NO‛。设计一个过程,判断字符串是否为数字串。解:DATASEGMENTSTRINGDB80,?,81DUP(?)YESDB0DH,0AH,"YES.$"NODB0DH,0AH,"NO.$"DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAH,0AHLEADX,STRINGINT21HMOVCL,STRING+1MOVCH,0MOVSI,2CALLEXAMCMPAH,0JENOMESS

LEADX,YESJMPDISPNOMESS:LEADX,NODISP:MOVAH,09HINT21HMOVAX,4C00HINT21HEXAMPROCMOVAH,1NEXT:MOVAL,STRING[SI]CMPAL,"0"JBEXITCMPAL,"9"JAEXITINCSILOOPNEXTJMPEXIT1EXIT:MOVAH,0EXIT1:RETEXAMENDPCODEENDSENDSTART36编写完整程序,调用READINT子程序,从键盘读入一个带符号整数,以二进制格式输出它的补码。解:INCLUDEYLIB.HDATASEGMENTNUMDW?PROMPT1DB0DH,0AH,"INPUTANUMBER:$"PROMPT2DB0DH,0AH,"THECOMPLEMENTIS:$"DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXLEADX,PROMPT1CALLREADINT

PUSHAXLEADX,PROMPT2MOVAH,09HINT21HPOPAXCALLDISPCALLCRLFMOVAX,4C00HINT21HDISPPROCMOVCX,16MOVBX,AXNEXT:ROLBX,1RCLDL,1ANDDL,01HORDL,30HMOVAH,02HINT21HLOOPNEXTRETDISPENDPCODEENDSENDSTART37设计一个子程序,求带符号字数组中绝对值最大的数,返回其地址和最大值。入口参数:DS:SI=数组首地址,CX=元素个数(大于0);出口参数:ES:DI=绝对值最大的数所在的地址,AX=绝对值最大的数;解:MAXABSPROCPUSHCXPUSHSIPUSHDSPOPESXORAX,AXNEXT:MOVBX,WORDPTR[SI]ANDBX,BXJZOK

NEGBXOK:CMPBX,AXJLESKIPMOVAX,BXMOVDI,SISKIP:ADDSI,2LOOPNEXTPOPSIPOPCXRETMAXABSENDP38编写一个子程序,以AX为入口参数,把AX中的各个二进制位颠倒次序后还放回AX中。例如,入口参数AX=1011000111101001B,处理后AX应为1001011110001101B。解:INVERTPROCPUSHCXPUSHBXMOVCX,16NEXT:ROLAX,1RCRBX,1LOOPNEXTMOVAX,BXPOPBXPOPCXRETINVERTENDP39编写子程序,入口参数是一个字型数据,存放在AX中,统计该字的16个二进制位中含有多少个1和多少个0。解:DATASEGMENTNUMDW1234HZERODB0ONEDB0DATAENDSCODESEGMENTASSUMEDS:DATA,CS:CODE

START:MOVAX,DATAMOVDS,AXMOVAX,NUMMOVCX,16CALLCOUNTMOVONE,ALMOVZERO,AHMOVAX,4C00HINT21HCOUNTPROCPUSHBXMOVBX,0NEXT:ROLAX,1ADCBX,0LOOPNEXTMOVBH,16SUBBH,BLMOVAX,BXPOPBXRETCOUNTENDPCODEENDSENDSTART40使用串操作指令,在STRING字符串中查找有无字符‘A’,如有将标志flag置1,否则将flag清0。答:程序如下:.MODELSMALL.DATASTRINGDB"ALLSTUDENTS$"FLAGDB0.CODESTART:MOVAX,@DATAMOVES,AXLEADI,STRINGMOVCX,FLAG-STRINGMOVAL,„A‟

CLDREPNZSCASBJZYESMOVFLAG,0JMPEXITYES:MOVFLAG,1EXIT:MOVAX,4C00HINT21HENDSTART41在STRING中查找空格,记下最后一个空格的位置,存放在变量SPACE中。如果没有空格,置SPACE为-1。答:程序如下:.MODELSMALL.DATASTRINGDB"THISISANEXAMPLE$"SPACEDW0.CODESTART:MOVAX,@DATAMOVDS,AXMOVSPACE,-1LEASI,STRINGCLDAGA:LODSBCMPAL,"$"JEOKENDCMPAL,„„JNZNEXTMOVSPACE,SIDECSPACENEXT:JMPAGAOKEND:MOVAX,4C00HINT21HENDSTART42两个字符串str1与str2以‚$‛字符结束,比较它们的字符是否相同,如果相同,在屏幕上显示‚Yes.‛,否则显示‚No.‛。答:程序如下:.MODELSMALL

.DATASTRING1DB"ALLSTUDENTS$"STRING2DB"ALLSTODENTS$"MESS1DB"YES.$"MESS2DB"NO.$".CODESTART:MOVAX,@DATAMOVDS,AXMOVES,AXLEASI,STRING1LEADI,STRING2CLDAGA:LODSBSCASBJNENOTSCMPAL,„$‟JNEAGAYES:LEADX,MESS1JMPEXITNOTS:LEADX,MESS2EXIT:MOVAH,09HINT21HMOVAX,4C00HINT21HENDSTART

习题五1.接口电路与外部设备之间传送的信号有哪几种?传输方向怎样?数据信号:对于输入设备,数据信号从外设通过接口送往总线,对于输出设备,数据信号从总线通过接口发往外部设备。状态信号:状态信号表明外部设备当前的工作状态,用来协调CPU与外部设备之间的操作。状态信号总是从外部设备通过接口发往总线。控制信号:控制信号是CPU向外设发出的命令,它指定设备的工作方式,启动或停止设备。控制信号从CPU通过接口发往外部设备。2.接口电路有哪些功能?哪些功能是必需的?接口电路可以具备:设备选择功能、信息传输功能、数据格式转换功能、联络功能、中断管理功能、复位功能、可编程功能和错误检测等功能。其中设备选择功能和信息传输功能是每一个接口电路所必备的。其他的功能是否需要则由设备的特点和工作方式决定。3.I/O端口的编址有哪几种方法?各有什么利弊?80X86系列CPU采用哪种方法?I/O端口的编址有两种不同的方式。I/O端口与内存统一编址:把内存的一部分地址分配给I/O端口,一个8位端口占用一个内存单元地址。已经用于I/O端口的地址,存储器不能再使用。I/O端口与内存统一编址后,访问内存储器单元和I/O端口使用相同的指令,这有助于降低CPU电路的复杂性,并给使用者提供方便。但是,I/O端口占用内存地址,相对减少了内存可用范围。而且,由于难以区分访问内存和I/O的指令,降低了程序的可读性和可维护性。I/O端口与内存独立编址:这种编址方法中,内存储器和I/O端口各自有自己独立的地址空间。访问I/O端口需要专门的I/O指令。80x86CPU采用I/O端口独立编址方式。4.按照传输信号的种类,I/O端口有几种?它们信号的传输方向怎样?按照传输信号的种类,I/O端口有三种:数据端口:数据信息从端口输入CPU(输入设备接口),或者从CPU写入端口(输出设备接口);状态端口:外设状态信息从端口输入CPU;控制端口:命令信息从CPU写入端口。5.I/O端口译码电路的作用是什么?在最小模式和最大模式下分别有哪些输入信号?I/O端口译码电路用于产生端口的读写选择信号。在最小模式下,译码电路接受来自总线的地址信号(16位),M/IO(=0),RD或者WR信号。最大模式下,译码电路接受地址

信号(16位),IOR或者IOW信号。6.外部设备数据传送有哪几种控制方式?从外部设备的角度,比较不同方式对外部设备的响应速度。外部设备数据传送有以下四种控制方式。直接传送方式(也称为无条件传送方式、同步传送方式):这种情况下,外部端口完全被动地等待CPU的访问,没有确定的响应速度,响应时间取决于CPU忙碌的程度以及程序对外部设备控制采取的策略。查询方式:如果CPU在某一时刻只对一个外设采用查询方式进行数据传输,CPU的响应延迟约为3~10个指令周期。响应速度快于中断方式,慢于DMA方式。中断方式:CPU的响应延迟平均为几十个指令周期,慢于查询方式,但是这种方式可以同时管理多个外部设备。DMA方式:外部端口的传输请求由DMA控制器响应,由于DMAC是一个专用于传输控制的电路,任务单一,不发生DMA传输竞争时,响应延迟仅为1~2个DMAC使用的时钟周期,远快于中断方式和查询方式。7.叙述一次查询式输出过程中,接口内各电路、信号的状态变化过程。一个数据的查询式输出过程由二个阶段组成:CPU从接口反复读取状态字:由地址译码电路产生状态端口选择信号,该信号不影响接口内部的状态。外部设备输出完成后,返回“确认”信号,该信号将状态寄存器相关位(READY)置位。如状态字表明外设已处于“就绪”状态,则向数据端口传送数据。由地址译码电路产生的数据端口选通信号一方面将数据总线上的数据写入数据寄存器,同时清除状态寄存器中的相关位(READY),向输出设备发出输出启动信号。有的输出接口设有控制端口,输出启动信号通过写控制端口产生。8.比较程序中断方式和查询方式的区别,根据比较,指出中断工作方式的优缺点。中断方式:外部设备工作完成后,通过“中断请求”信号“主动”向CPU“报告”。查询方式:外部设备工作完成后,状态信号储存在接口电路内,被动地等待CPU来读取。根据上述比较,可以得到中断工作方式的如下特点:优点:1)CPU能够及时了解外部设备的状态,从而对外部设备IO请求进行及时处理。2)由于CPU“被动”地等待外部设备的“中断请求”,外部设备进行输入/输出操作时,CPU可以同时执行其他的程序,CPU和外部设备“并行”工作。3)由于同样的原因,在中断方式下,CPU可以同时管理多台外部设备,CPU的效率得到提高。缺点:1)用中断方式需要CPU增加相应的管理逻辑,增加了CPU电路的复杂性。2)由于CPU“被动”地接收“中断请求”信号,CPU必须通过与外部的一个联络过

程才能知道是那一个设备在申请中断,这增加了响应时间。为了从当前任务转移到中断服务,CPU必须保护原有的运行环境,进行“任务”的“切换”,这也会增加响应时间。3)有较多的设备使用中断方式时,会产生“中断申请”的“竞争”。这一方面降低了响应速度,另一方面增加了管理的复杂性。9.比较DMA方式和程序中断方式的区别,根据比较,指出DMA工作方式的优缺点。中断方式:外部设备每进行一个数据的输入/输出,都要通过“中断申请”要求CPU进行处理。CPU通过执行一段“中断服务程序”完成数据的传输。DMA方式:CPU通过对DMAC的初始化,启动一个数据块的传输操作。之后的数据传输通过信号的联络,在外设接口和存储器之间进行,CPU只需简单地让出总线,而无需其他操作。根据上述比较,可以得到DMA工作方式的如下特点:优点:1)对于CPU而言,它的任务仅仅是在一个数据块传输之前对DMAC进行初始化,CPU用于传输控制的操作达到最小(不考虑与通道/IO处理器方式的比较),CPU的效率最高。CPU与外设“并行”工作。2)外部设备一个数据输入/输出完成后,向DMAC申请进行数据传输,响应时间仅为DMAC的1~3个时钟周期。响应速度达到最快,可以满足高速传输的需要。缺点:1)实现DMA控制需要增加DMA控制器和总线控制逻辑,增加了系统的复杂性。2)DMA传输需要占用总线,并且具有较高的“优先级”。这使得系统对其他设备的响应速度不能得到明确的保证。10.某输入设备接口数据端口、状态端口、控制端口地址分别为70H,71H,72H。状态端口D5=1表示输入完成,控制端口D7=1表示启动设备输入(输入完成后由设备清除该位)。从该设备输入100个字节数据,存入以BUFFER为首地址的缓冲区。如果启动该设备1秒后仍未完成一次输入,则视为超时错,显示出错信息后返回。分别用8086汇编语言和C语言编写完成上述功能的I/O程序。汇编语言程序:DATASEGMENTBUFFERDB100DUP(?)ERRORDB13,10,“OVERTIME!”,13,10,“$”DATAENDS;CODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATA

MOVDS,AXMOVCX,100LEABX,BUFFERONE:XORDX,DX;DX用作响应计时器,初值0MOVAL,80HOUT72H,AL;启动输入W:INAL,71HINCDX;记录延迟时间TESTAL,00100000B;测试完成位JNZREAD;输入完成,转READ读取数据CMPDX,50000;假设循环50000次时间为1秒JBW;未超时,继续测试JMPOVERTIME;超过1秒,报告出错READ:INAL,70H;读入数据MOV[BX],AL;数据存入缓冲区INCBX;修改指针LOOPONE;100个数据尚未输入完成,转ONE继续JMPDONE;100个数据输入完成,转DONE结束程序OVERTIME:LEADX,ERRORMOVAH,9INT21H;响应超时,显示出错信息DONE:MOVAX,4C00HINT21H;返回OSCODEENDSENDSTARTC语言程序:main(){inti,status,time,buffer[100];for(i=0;i<100;i++){outportb(0x72,0x80);/*启动输入*/for(time=0;time<20000;time++){status=inportb(0x71);/*读状态*/if(status&0x20){buffer[i]=inportb(0x70);exit;}/*读数据,保存*/}if(time>=20000){printf(“nOverTime!n”);exit;}/*超时报错*/}}

11.某输出设备数据端口、状态端口地址分别为220H,221H。状态端口D0=1表示输出完成。将数据段中以STRING为首地址的20个字符(用七位ASCII代码存储)添加水平和垂直校验发送到该外部设备。用8086汇编语言编写完成上述功能的I/O程序。汇编语言程序:DATASEGMENTSTRINGDB20DUP(?)SUMDB0DATAENDS;CODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVCX,20LEABX,STRINGMOVSUM,0;垂直校验码初值为0ONE:MOVDX,221H;DX置为状态端口地址INAL,DXTESTAL,00000001B;测试输出完成位JZONE;未完成,转ONE继续读取状态MOVAL,[BX];从字符串取出一个字符的ASCII代码ANDAL,07FH;清除最高位,准备置入校验位JPEOUTPUT;判代码奇偶属性,ORAL,80H;奇数个“1”,最高位置1(偶校验)OUTPUT:MOVDX,220HOUTDX,AL;输出添加了校验位的代码XORSUM,AL;生成垂直校验位INCBX;修改指针LOOPONE;20个数据尚未输出完成,转ONE继续MOVDX,221H;输出垂直校验代码LAST:INAL,DXTESTAL,00000001BJZLASTMOVAL,SUMMOVDX,220HOUTDX,ALDONE:MOVAX,4C00HINT21H;返回OS

CODEENDSENDSTART12.试画出矩阵式键盘查询的程序流程图。行扫描法键盘扫描流程键盘扫描码=0,计数器=8行扫描代码=11111110B向行线端口输出行扫描代码(7行为1,1行为0)从列线端口读入Y全“1”N将行扫描代码左移一位键盘扫描码+8列线读入代码右移1位计数器-1NN计数器=0进位=0YY键盘扫描码+1键盘扫描码=11111111B返回上述流程中假设键盘为8×8结构,如果有键按下,返回它的8位扫描码。其中:最低3位为该键所在列,次低3位为该键所在行,最高2位为0。如果没有键按下,返回8位“1”。13.试画出公用端口多位LED输出的程序流程图。

共用端口LED扫描流程SI=缓冲区首址,CX=8BX=七段码表首址,位码=80H位码输出全“0”,熄灭各LED从缓冲区取出一个字节转换成七段码七段码送段码端口输出位码点亮一个LED修改位码修改输出缓冲区指针延时N循环8次结束Y返回

习题六1.什么叫中断?有哪几种不同类型的中断?由于某个事件的发生,CPU暂停当前正在执行的程序,转而执行处理该事件的一个程序。该程序执行完成后,CPU接着执行被暂停的程序。这个过程称为中断。根据中断源的位置,有两种类型的中断。有的中断源在CPU的内部,称为内部中断。大多数的中断源在CPU的外部,称为外部中断。根据中断引脚的不同,或者CPU响应中断的不同条件,也可以把中断划分为可屏蔽中断和不可屏蔽中断两种。2.什么是中断类型?它有什么用处?用若干位二进制表示的中断源的编号,称为中断类型。中断类型用来区分不同的中断,使CPU能够在中断响应时调出对应的中断服务程序进行中断处理。3.有哪几种确定中断优先级的方法?说明每一种方法各自的优劣之处。确定中断优先权有四种可选的方法。(1)软件查询法:采用程序查询的方法确定中断服务的顺序。这种方法中断逻辑最简单(基本上不需要外部中断逻辑),优先级可以灵活设置,但中断响应所需时间最长。(2)分类申请法:CPU分设二个中断申请信号的输入引脚。这种方法需要CPU提供条件。(3)链式优先权排队:菊花链法。这种方法需要的外部中断逻辑比较简单,容易实现,但是设备较多时信号延迟大,对设备故障敏感。(4)可编程中断控制器:“向量”优先权排队专用电路。这种方法功能最全面,控制灵活,可以通过程序设定中断优先权为固定的或循环的,但需要增加专用的中断控制器。4.什么是中断嵌套?使用中断嵌套有什么好处?对于可屏蔽中断,实现中断嵌套的条件是什么?CPU在处理级别较低的中断过程中,出现了级别较高的中断请求。CPU停止执行低级别中断的处理程序而去优先处理高级别中断,等高级别中断处理完毕后,再接着执行低级别的未处理完的中断处理程序,这种中断处理方式称为多重(级)中断或中断嵌套。使用中断嵌套可以使高优先级别的中断得到及时的响应和处理。对于可屏蔽中断,由于CPU在响应中断时已将IF清零,所以一定要在中断处理程序中加入开中断指令,才有可能进行中断嵌套。5.什么叫中断屏蔽?如何设置I/O接口的中断屏蔽?用程序的方法使某些中断源的中断请求不能够发送到CPU,或者虽然能够发送但是不能

得到响应,这种方法称为中断屏蔽。在外设的接口内增设一个中断屏蔽触发器(可以用D触发器实现),该触发器的Q端与中断请求信号相“与”后连接到INTR。当Q=0时,中断请求不能发往INTR。通过设定中断屏蔽触发器的状态,可以控制中断请求信号是否能够送到INTR端。置IF=0,可以使80x86CPU不响应来自INTR的可屏蔽中断请求。6.什么是中断向量?中断类型为1FH的中断向量为2345H:1234H,画图说明它在中断向量表中的安置位置。中断服务程序的入口地址称为中断向量。中断类型为1FH,0000:007CH34H它的中断向量放置在1FH×4=0000:7CH开始的位置上。如右0000:007DH12H图。0000:007EH45H0000:007FH23H7.叙述一次可屏蔽中断的全过程。(1)中断源请求中断外部中断源通过INTR引脚向CPU请求中断。(2)中断响应中断源提出中断请求后,如果CPU处于允许中断状态(IF=1);没有不可屏蔽中断请求和总线请求;当前指令执行结束。则转入中断响应周期。在中断响应周期:CPU取得中断源的中断类型;将标志寄存器FLAGS和CS、IP(断点)先后压入堆栈保存;清除自陷标志位TF和中断允许标志位IF;读中断向量表,获得相应的中断服务程序入口地址,转入中断服务程序。(3)中断服务中断服务程序的主要内容包括:保护现场开中断中断处理关中断恢复现场(4)中断返回8.简要叙述8259A内部IRR,IMR,ISR三个寄存器各自的作用。三个寄存器长度均为8位。IRR用来记录引脚IR7~IR0上由外部设备送来的中断请求信号。当外部中断请求线IRi变为有效时,IRR中与之对应的第i位被置1。IMR用于设置对中断请求的屏蔽信号。此寄存器的第i位被置1时,与之对应的外部中

断请求线IRi被屏蔽,不能向CPU发出INT信号。可通过软件设置IMR内容,确定每一个中断请求的屏蔽状态。ISR用于记录当前正在被服务的所有中断级,包括尚未服务完而中途被更高优先级打断的中断级。若CPU响应了IRi中断请求,则ISR中与之对应的第i位置1。ISR用于中断优先级管理。9.8259A是怎样进行中断优先权管理的?8259A通过以下两种途径实现对中断优先权的管理:(1)通过设置中断屏蔽寄存器IMR,可以屏蔽某些中断请求,从而动态地改变各请求端的优先级别。(2)8259A响应某个中断请求之后,将ISR寄存器对应位置1。如果后续的中断请求级别低于正在响应的中断请求,则该中断不能立即被响应。反之,如果新的中断请求级别高于正在响应的中断请求,则允许进行中断嵌套。中断服务结束时,应将ISR寄存器对应位清零。10.特殊全嵌套方式有什么特点?它的使用场合是什么?特殊全嵌套方式一般用于级联方式下的8259A主片。如果8259A主片在一次中断处理尚未结束时,收到了来自同一个引脚的第二次中断请求,并且该8259A采用普通全嵌套方式,则它不会响应来自同一个引脚的第二次中断请求。如果该8259A采用特殊全嵌套方式,就会响应该请求(中断嵌套),从而可以及时响应连接在同一从片8259A上,并且相对有较高优先级别的中断请求。11.向8259A发送‚中断结束‛命令有什么作用?8259A有哪几种中断结束方式?分析各自的利弊。中断服务完成时,必须给8259A一个命令,使这个中断级别在ISR中的相应位清“0”,表示该中断处理已经结束,允许响应新的较低级别的中断。这个命令称为“中断结束”命令。8259A有两种不同的中断结束方式。(1)自动中断结束方式(AEOI)8259A在中断响应周期内自动清除ISR中对应位。这种方式使用简单,但是不能充分实现中断的优先权管理。这种方式只能用在系统中只有一个8259A,且多个中断不会嵌套的情况。(2)非自动中断结束方式(EOI)从中断服务程序返回前,在程序里向8259A输出一个中断结束命令(EOI),把ISR对应位清“0”。这种方式可以有效地实现中断优先权的管理,从而保证高优先级的中断可以得到及时响应。但是,如果在程序里忘了将ISR对应位清零,那么,8259A将不再响应这个中断以及比它级别低的中断请求。12.某系统中有两片8259A,从片的请求信号连主片的IR2引脚,设备A中断请求信号连从片IR5引脚。说明设备A在一次I/O操作完成后通过两片8259A向8086申请中断,

8086CPU通过两片8259A响应中断,进入设备A中断服务程序,发送中断结束命令,返回断点的全过程。设备A通过从片IR5引脚向从片发出中断请求;从片将IRR5置“1”,并通过INT(与主片IR2相连)向主片发出中断请求;主片将IRR2置“1”,通过INT(与CPU的INTR相连)向CPU发出中断请求;CPU通过第一个INTA向主片和从片响应中断请求;主片8259A在CAS0~CAS2上发出代码“010”,表示连接在IR2上的从片中断被响应,同时主片还把本片ISR2置“1”,把本片IRR2清“0”;从片收到第一个INTA和主片CAS0~CAS2上发来的010代码后,将本片ISR5置“1”,同时把本片IRR5清“0”。收到第二个INTA后,将本片IRR5对应的中断类型通过数据总线发往CPU;CPU进入设备A的中断服务程序,在程序中先后对主片和从片发出中断结束命令,两个芯片内的ISR2和ISR5先后被清零。中断服务结束,返回断点继续执行。13.某8086系统用3片8259A级联构成中断系统,主片中断类型号从10H开始。从片的中断申请连主片的IR4和IR6引脚,它们的中断类型号分别从20H、30H开始。主、从片采用电平触发,嵌套方式,普通中断结束方式。请编写它们的初始化程序。假设主片端口地址为10H,12H。从片的端口地址分别为18H,1AH和1CH,1EH。……MOVAL,00011001B;主片ICW1OUT10H,AL;电平触发,级连方式MOVAL,10H;主片ICW2OUT12H,AL;主片中断类型MOVAL,01010000B;主片ICW3OUT12H,AL;IR4,IR6连有从片MOVAL,00010001B;主片ICW4OUT12H,AL;特殊全嵌套,非自动中断结束MOVAL,00011001B;从片ICW1OUT18H,AL;电平触发,级连方式MOVAL,20H;从片ICW2OUT1AH,AL;从片中断类型MOVAL,00000100B;从片ICW3OUT1AH,AL;本片连接在主片IR4引脚上MOVAL,00000001B;从片ICW4OUT1AH,AL;非特殊全嵌套,非自动中断结束

MOVAL,00011001B;从片ICW1OUT1CH,AL;电平触发,级连方式MOVAL,30H;从片ICW2OUT1EH,AL;从片中断类型MOVAL,00000110B;从片ICW3OUT1EH,AL;本片连接在主片IR6引脚上MOVAL,00000001B;从片ICW4OUT1EH,AL;非特殊全嵌套,非自动中断结束注意:(1)由于8086系统有16根数据线,各8259A的端口地址均为偶数(假设各8259A的数据线连接在8086系统的低8位数据线上)。(2)主片用特殊全嵌套,从片用一般全嵌套。14.给下面的8259A初始化程序加上注释,说明各命令字的含义。MOVAL,13H;ICW1:边沿触发,单片8259AOUT50H,AL;MOVAL,08H;ICW2:中断类型高5位为00001OUT51H,AL;MOVAL,0BH;ICW4:非特殊全嵌套,缓冲方式,主片,非自动中断结束OUT51H,AL;15.设8259A端口地址为20H和21H,怎样发送清除ISR3的命令?为了清除ISR3,需要通过OCW2发送特殊的中断结束命令,使SL=1,EOI=1,L2L1L0=011。指令如下:MOVAL,01100011BOUT20H,AL16.图4-17能否直接用于8086系统?为什么?图4-17不能直接用于8086系统,原因是:(1)多个设备的中断请求如果直接送往CPU,应采用“线或”的方法,每个接口的中断请求信号应由“OC门(集电极开路门)”以“负逻辑”的方式连接,如下图。

+5VCPUOC门OC门...OC门设备1设备2设备n中断请求中断请求中断请求(2)电路没有解决中断优先权的问题。CPU用INTA信号响应中断时,会将所有正在申请中断的接口的请求信号清除。加接“菊花链”可以解决该问题。(3)电路没有解决中断类型的发送问题,需要增加相关电路。例如,把设备接口的INTR连接到8259A。

习题七1.8255A的方式选择控制字和C口按位控制字的端口地址是否一样,8255A怎样区分这两种控制字?写出A端口作为基本输入,B端口作为基本输出的初始化程序。解:(1)8255A的方式选择控制字和C口按位控制字的端口地址一样,它们之间的区别在控制字的D7位(特征位)的值不同,8255A的方式选择控制字D7=1,而C口按位置位/复位控制字D7=0。(2)初始化程序:(设端口地址为,A口:200H,B口:201H,控制口:203H)MOVAL,90HMOVDX,203HOUTDX,AL2.用8255A的A端口接8位二进制输入,B端口和C端口各接8只发光二极管显示二进制数。编写一段程序,把A端口读入的数据送B端口显示,而C端口的各位则采用置0/置1的方式显示A端口的值。解:(设端口地址为,A口:200H,B口:201H,C口:202H,控制口:203H)MOVAL,90H;8255A初始化:MOVDX,203H;8255A各组方式0,A口输入OUTDX,AL;B、C口输出MOVDX,200HINAL,DX;读A口输入值MOVDX,201HOUTDX,AL;送B口输出MOVAH,AL;A口输入值转存在AH中MOVDX,203HMOVCX,08;CX置循环次数初值MOVAL,00H;C端口置0/置1控制字初值LPA:ANDAL,0FEH;清除最低位SHRAH,1;A端口一位转入CFADCAL,0;A端口一位从CF转入命令字OUTDX,AL;A端口一位从送往C端口对应位ADDAL,02H;形成下一个命令字LOOPLPA;处理C端口下一位

3.将8255A用作两台计算机并行通信的接口电路,请画出采用查询式输入/输出方式工作的接口电路,并写出采用查询式输入/输出方式的程序。解:用两片8255作两台计算机8088_A与8088_B之间并行通信的接口电路,两片8255之间的连接如下图所示。两片8255均在方式1、查询方式下工作。D7~D08255A8255BD7~D0A口A口A口82558088-APC48088-BAPC0地址(STB)地址CSB口CS译码PC6译码PC0A0A0(ACK)A0A0A1A1A1A1(1)8088_A输出程序:(8255_A的A口作为数据输出口,C口的PC0作为“数据输出选通”信号,负脉冲输出。C口的PC6作为“应答”信号输入,负脉冲有效。端口地址:A口:200H,C口:202H,控制口:203H)DATASEGMENTBufferDB“Thisisaexample.”,0DH,0AH,-1DATAENDSCODESEGMENTSTART:MOVAX,DATAMOVDS,AXLEABX,Buffer;输出缓冲区指针送BXMOVDX,203HMOVAL,0A0H;8255_A的方式选择字,A口工作在方式1、输出,C口低四位输出OUTDX,ALMOVAL,1OUTDX,AL;将PC0置1CALLDELAY;延时等待对方完成初始化;A口查询方式输出NEXT:MOVDX,202HINAL,DLTESTAL,80H;判别OBF是否有效JZNEXT;数据尚未取走,等待MOVDX,200H

MOVAL,[BX]OUTDX,AL;输出一项数据INCBXMOVDX,203HMOVAL,0OUTDX,ALNOPNOPINCALOUTDX,AL;通过PC0向对方发选通信号(负脉冲)CMPBYTEPTR[BX-1],-1;判断输出是否完成JNENEXT;未完成,继续MOVAX,4C00HINT21HCODEENDSENDSTART(2)8088_B输入程序:(8255_B的A口作为输入,方式1,PC4作为“数据输入选通”信号,输入,负脉冲有效。PC0为“应答”信号输出,负脉冲有效。端口地址:A口:210H,C口:212H,控制口:213H)DATASEGMENTBufferDB80DUP(?)DATAENDS;CODESEGMENTSTART:MOVAX,DATAMOVDS,AXLEABX,Buffer;输入缓冲区指针送BXMOVDX,213HMOVAL,0B0H;8255_B的方式选择字,A口工作在方式1,输入,C口低四位输出。OUTDX,ALMOVAL,01HOUTDX,AL;PC0置1,表示没有“应答”信号CALLDELAY;延时等待对方状态就绪;A口查询方式输入AGA:MOVDX,212H

INAL,DXTESTAL,20HJZAGA;PC5(IBF)是否为1,不是,无数据输入,继续查询MOVDX,210HINAL,DXMOV[BX],ALMOVDX,212HMOVAL,0OUTDX,ALINCBXNOPNOPINCALOUTDX,AL;通过PC0向发送方发“应答”负脉冲CMPBYTEPTR[BX-1],-1;数据接收完了吗?JNEAGA;未完,继续MOVAX,4C00HINT21HCODEENDSENDSTART说明:这道题有多种可选的解法,上面的方法是程序比较简单的一种。这种方法实施时,应先启动8088B,使它首先“就绪”,然后开始通讯。由于双方都用负脉冲进行选通,联络过程比较简单,也比较可靠。可选的另一种方法是:在上述连接的基础上用中断方式进行数据传输,以提高CPU的工作效率。需要编制双方的中断服务程序,初始化时要设置中断向量,允许8255中断,开放中断等操作。当然也要连接相应的中断请求信号线。可选的第三种方法是:双方用一根状态线(C端口某一位)送往对方,用这两根线进行联络(“握手”)。这种方法看似简单,其实程序是比较复杂的。双方联络的过程如下图。A状态②③⑤数据④①⑥B状态

8088B在初始化完成后,把它的状态线置为“高电平”,表示可以开始接受数据。而8088A在初始化完成后,把它的状态线置为“低电平”,表示数据传输尚未开始。①8088A查询8088B的状态,在发现8088B“就绪”(状态线为高电平)后,把数据发往8255的(A或B)端口。②8088A发出数据之后把本机状态置为“就绪”(高电平),表示数据已经送到端口的数据线上。③8088B查询8088A的状态,得知8088A的状态线“就绪”,知道8088A已经把数据送出,于是从8255接收数据,并把自身的状态线置为“未就绪”,表示已经把8088A发出的数据接收。④8088A查询到8088B的状态线变为低电平,知道对方已经把数据接收完成,于是把本机的状态线置为“低电平”,表示这个数据的发送已经完成,而下一个数据尚未发出。⑤8088B查询到8088A的状态线变为“低电平”,知道对方已经结束了第一个数据的传输,在本机做好下一个数据的接收准备之后(例如,把数据存入缓冲区,如果缓冲区满,则把缓冲区内容存入磁盘文件),把本机状态线置为“高电平”,表示已经做好了接收下一个数据的准备。⑥8088A得知8088B做好准备,发送下一个数据。于是,下一个数据的传输可以由此开始(转①)。这种方法实施时,应首先启动8088A。4.设计一个用8255A作为8个七段显示器的接口电路,并设计一个把内存地址为ADDRA的8个数字在这8个七段显示器上显示的程序。解:设8个七段显示器采用共阳接法,A口控制段的显示,B口控制位的显示。端口地址A口:200H,B口:201H,控制口:203HDATASEGMENTADDRADB×,×,×,×,×,×,×,×TABLEDB40H,4FH,24H,30H,19HDB12H,02H,78H,00H,10HDISPBITDB?DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATASTART:MOVAX,DATAMOVDS,AXMOVAL,80H;对8255A初始化,方式0,输出MOVDX,203HOUTDX,ALLEABX,TABLE;BX置为七段码表首地址

MOVDISPBIT,7FH;置位码初值为7FHLEASI,ADDRA;SI置为显示缓冲区首地址MOVCX,8;CX置为循环次数初值8AGA:MOVAL,0FFHMOVDX,201HOUTDX,AL;熄灭所有数码管MOVAL,[SI];取出一个待显示数XLAT;转换成七段码MOVDX,200HOUTDX,AL;送入段码端口MOVAL,DISPBIT;MOVDX,201HOUTDX,AL;送当前位码,点亮一个数码管RORDISPBIT,1;产生下一个位码INCSI;修改指针,指向下一个待显示数据CALLDELAY;延时LOOPAGA;处理下一个数码管的显示MOVAX,4C00HINT21HCODEENDSENDSTART5.8254定时/计数器的定时与计数方式有什么区别?8254在方式0工作时,各通道的CLK、GATE信号有什么作用?各通道的控制字地址都相同,8254是怎样区分的?解:(1)8254作为计数器使用时,对CLK端的输入脉冲进行单纯的减法计数,这时CLK端输入的脉冲不作为计时基准。此外,用作计数器时,计数完成后必须重新初始化,只能使用一次。8254作为定时器使用时,要求CLK端输入的脉冲必须作为时钟基准,通过对该基准时钟脉冲的计数来实现精确定时。用作定时器时,计数的过程周而往复,重复进行。(2)8254工作在方式0时,CLK端输入计数用的脉冲信号;GATE信号为高电平时,对CLK端输入的脉冲进行计数;GATE信号为低电平时,暂停计数;GATE信号重新为高电平后,恢复原先的计数。(3)由8254的方式控制字中的D7、D6两位来选择计数通道。6.设8254的端口地址为0240H~0243H,通道0输入的CLK频率为1MHz,为使通道0输出1KHz的方波,编写初始化程序。如果让通道0与通道1级联(即OUT0

接CLK1)实现1秒钟定时,则初始化程序如何编制。解:(1)通道0输出1KHz的方波:计数初值为1MHz/1KHz=1000,等于十六进制数03E8H,控制字设定为先写低8位,后写高8位,方式3工作,二进制计数方式,所以控制字为36H。初始化程序如下:MOVAL,36H;MOVDX,243H;写入通道0的控制字OUTDX,AL;MOVDX,240H;MOVAL,0E8H;写入通道0的时间常数OUTDX,AL;MOVAL,03H;OUTDX,AL;(2)通道0与通道1级联实现1秒定时:要实现1秒定时,对1MHz输入脉冲进行分频的系数为1000000=5000×200。通道0工作在方式2,分频系数200,采用十进制计数,则通道0方式控制字为:25H。通道1工作在方式0,分频系数5000,也采用十进制计数,则通道1方式控制字为:61H。初始化程序如下:MOVAL,25H;通道0控制字:方式2,十进制计数,只写高8位MOVDX,243H;OUTDX,AL;MOVAL,61H;通道1控制字:方式0,十进制计数,只写高8位OUTDX,AL;MOVDX,0240H;MOVAL,02H;通道0时间常数(BCD数高8位)OUTDX,AL;MOVAL,50H;通道1时间常数(BCD数高8位)MOVDX,0241H;OUTDX,AL;如果要再次进行1秒钟定时,则需要对通道1重新初始化。如果需要连续的1秒定时信号,则通道1应选用方式3。对总数为1000000的分频系数,可以有多种分解方法。7.编制一个使PC机的8254产生600Hz方波的程序,并使该方波送至扬声器发声。解:PC机中利用8254定时器的通道2来驱动扬声器。通道2的工作及其输出受到主板上8255A的PB口(口地址61H)控制:GATE2接PB0,即PB0=1时,定时器才可能工作;OUT2与PB1相与后输出到扬声器,即PB1=1时,定时器2的OUT2才能输

出到扬声器。定时器的输出波形是对1.1931MHZ频率信号分频得到的,因此将定时器2工作在方式3,分频系数用下式计算:分频系数=1193100÷给定频率(1193100=12348CH)因此程序如下:MOVAL,0B6H;通道2控制字:方式3,16位常数OUT43H,AL;送入8254控制端口MOVDX,12H;MOVAX,348CH;DX,AX中置入常数12348CHMOVDI,600;DI为输出频率DIVDI;除法运算,计算分频系数OUT42H,AL;低8位送通道2MOVAL,AH;OUT42H,AL;高8位送通道2INAL,61H;ORAL,3;OUT61H,AL;将8255A的B端口低2位置“1”8.在RS-232C接口标准中,引脚TxD、RxD、RTS、CTS、DTR、DSR、的功能是什么?解:TxD:串行数据输出。RxD:串行数据输入。DTR:数据终端准备好状态,低电平有效。用于向调制解调器或外设表示数据终端已准备好。——DSR:数据设备准备好状态,低电平有效。调制解调器或外设准备好时DSR有效。RTS:请求发送信号,低电平有效。表示数据终端设备已经做好发送数据的准备,请调制解调器/外设准备接收数据。CTS:清除发送(允许传送)信号,低电平有效。调制解调器/外设作好传送准备,允许数据终端设备发送数据时CTS有效。9.16550的通信控制寄存器中的寻址位有什么作用?在初始化编程时,应该怎样设置?解:16550芯片内,接收缓冲寄存器/发送保持寄存器的地址与除数低字节寄存器的地址相同,中断允许寄存器的地址与除数高字节寄存器的地址相同。为了区分同一地址的不同用途,16550使用DLAB位来加以标识。DLAB位是通信线控制寄存器的最高位D7,该位设置为0,随后的相应操作对接收缓冲寄存器/发送保持寄存器或中断允许寄存器进行;该位设置为1,随后的相应操作对除数寄存器进行。在向除数寄存器写入初值之前,应将DLAB置为1。由于一般不需要重复访问除数寄存器,写完除数后应将DLAB置为

0,以方便后续的操作。10.编写用PC机中16550查询方式输入50个字符的异步通信程序。设16550的端口地址为3F8H~3FFH,数据格式为:8位数据位、1位偶校验位、2位停止位,通信速率为19.2Kbps。解:接收子程序中,如果接收成功,清CF标志,否则,置位CF标志位。程序如下:;16550查询方式接收程序DATASEGMENTREC_DATADB50DUP(?);存放接收的数据TIMESDW50;要接收的数据个数DATAENDSCODESEGMENTASSUMECS:CODE,DS:DATABEGIN:MOVAX,DATAMOVDS,AX;初始化16550MOVDX,03FBH;16550控制寄存器地址送DXMOVAL,80H;置DLAB=1,设置除数寄存器OUTDX,ALMOVAX,003CH;波特率为19200bps时,除数为003CHMOVDX,03F8H;除数寄存器地址送DXOUTDX,ALMOVAL,AHINCDXOUTDX,ALMOVAL,1FH;8位数据位,偶校验,2位停止位MOVDX,03FBH;16550控制寄存器地址送DXOUTDX,AL;写入控制字„„CALLRECEIVE„„MOVAH,4CH;程序结束,返回操作系统INT21H;查询方式接收子程序RECEIVEPROCNEARLEABX,REC_DATA;接收缓冲区首地址送BXMOVCX,TIMES;要接收的数据个数送CXREPIN:MOVDX,03FDH;通信状态寄存器地址送DX

INAL,DXTESTAL,1EH;检测接收过程有无错误JNZERRORTESTAL,01H;检测接收缓冲器中是否有数据JZREPIN;没有数据,继续检测MOVDX,03F8H;数据接收寄存器地址送DXINAL,DXMOV[BX],ALINCBXLOOPREPINCLC;接收成功,清CF标志位JMPDONEERROR:STC;接收不成功,置CF标志位DONE:RETRECEIVEENDPCODEENDSENDBEGIN11Intel8251A与16550芯片相比较,有些什么不同之处?答:两个芯片的主要区别是:(1)16550芯片只能进行异步串行通讯,而Intel8251A不仅可以进行异步串行通讯,而且也可以用于同步串行通讯。(2)Intel8251A芯片没有内部的波特率发生电路,因此,它所需要的发送、接收时钟信号只能依赖外部提供。12为什么Intel8251A芯片初始化时需要先送3个00H,1个40H?是否每次都需要?答:由于Intel8251A只使用两个端口地址,所有的控制信息都写入同一个地址的端口内。这样,所有的控制信息必须按照一定的顺序写入,否则就会产生错误。为了保证初始化时,Intel8251A芯片处于初始的状态,可以向Intel8251A先送3个00H,1个40H。如果程序能够确保Intel8251A已经处于初始状态,那么这项操作是可以省略的。

习题八1.什么是DMA传输?DMA传输有什么优点?为什么?所谓直接存储器传送(DMA)是指将外设的数据不经过CPU直接送入内存储器,或者,从内存储器不经过CPU直接送往外部设备。使用DMA传输之后,每个数据的传输过程不需要CPU参与,在DMA控制器的控制下,在一个DMA总线周期里完成数据在外部接口和存储单元之间的直接传输。所以使用DMA传输既可以减轻CPU的负担,又可以缩短系统对外部设备的响应时间,提高数据传输速率。2.叙述一次数据块DMA传输和一个数据DMA传输的全过程。一次数据块DMA传输的全过程:程序对DMA控制器进行初始化,写入存储器数据块首地址,传输字节数,传输方向等信息。同时启动外部设备(例如,启动输出设备进行第一次输出);外部设备每完成一次输入/输出,它的完成信号通过DMA控制器启动一次DMA数据传输;全部预设的数据传输完成,DMA控制器发出“传输完成”信号,向CPU申请中断。CPU在中断服务程序中设置完成标志,或者对DMA控制器进行下一次初始化。一个数据DMA传输的全过程。外设准备就绪,需要进行DMA操作时,向DMA控制器发出“DMA请求信号”。DMA控制器接到此信号后,向CPU发“总线请求信号”。CPU接到总线请求信号,在当前总线周期结束后,发出“DMA响应信号”。DMAC向外部设备发出“外设读”或“外设写”控制信号,向存储器发出“存储器写”或“存储器读”控制信号,同时发出存储单元地址。在这二个信号的作用下,一字节的数据从外设接口通过数据总线送往存储单元,或者从存储单元送往外设接口。传送1个字节之后,DMAC自动修改内部地址寄存器和字节计数器的内容。DMA控制器撤销“总线请求信号”,CPU也撤销“总线应答”信号。3.什么叫DMA通道?它如何组成?DMA通道是控制一个外设接口和存储器进行DMA传输的相关电路的总和。每个通道包括地址寄存器、字节计数器、方式寄存器、DMA请求触发器、屏蔽触发器、状态寄存器以及所需的其他控制电路。4.DMA控制器8237A的成组传送方式和单字节传送方式各有什么特点?它们的适用范围各是什么?成组传送方式下,DMA控制器获得总线控制权后,可以连续进入多个DMA周期,进行多个字节的传输。这种方式可以获得最高的数据传输速度。在数据传输期间,CPU不能访问

总线。如果一次传输的数据较多,这种方式会对系统工作产生一定的影响。成组传送方式适用于外部设备要求很高的传输速率,系统其他负担较轻,连续占用总线不会产生严重后果的情形。在单字节传输方式下,8237A完成1个字节传输后都释放系统总线,一次DMA传输结束,CPU可以在每个DMA周期结束后控制总线。这种方式适用于外部设备的传输速率要求不太高,或者系统不允许有较长时间停顿的情况。5.怎样用指令启动一次DMA传输?怎样用指令允许/关闭一个通道的DMA传输?用指令将DMA请求寄存器中相关位置位,可以启动一次DMA传输。用指令将DMA屏蔽寄存器中相关位复位,可以允许一个通道的DMA传输。将DMA屏蔽寄存器中相关位置位,可以关闭一个通道的DMA传输。6.DMA控制器8237A能不能用中断方式工作?请说明。DMA控制器8237A可以用中断方式工作。将8237A的EOP信号反相后连接到中断控制器的中断请求输入端,则一次数据块传输结束后,可以向CPU申请中断,由专门的中断服务程序进行结束处理。7.如何判断某通道的DMA传输是否结束?有几种方法可供使用?判断某通道的DMA传输是否结束有二种方法。其一是读出DMA控制器的状态寄存器内容,测试其中代表该通道的状态位,可以得知该通道的DMA传输是否结束。其二是读出该通道的字节计数器内容,如果值为0(对8237A而言为-1),表示该通道的DMA传输已经结束。此外,可以用8237A的EOP信号向CPU申请中断。一旦进入这个中断服务程序,表明该通道的DMA传输已经结束。8.叙述一次DMA控制器8237A编程使用的主要步骤。DMA控制器8237A初始化编程的主要步骤为:发复位命令;写命令字,设置8237A的工作方式;写方式字,设置需使用的通道的工作方式;清除先/后触发器;写入内存储器起始地址;写入传送的字节数-1;清除该通道的屏蔽位;启动外部设备,如果是内存到输出设备,用指令设置第一次DMA请求。

9.使用DMA控制器8237A传输一个字节需要多少时间?受那些因素影响?请作具体分析。使用DMA控制器8237A传输1字节数据需要4个DMA控制器使用的时钟周期,对于速度稍慢的外设/存储器,也可以插入一个或多个等待周期。影响DMA周期时间长短的因素有:DMA控制器使用的时钟频率:频率越高,DMA周期越短;存储器和外部设备的工作速度:如果速度跟不上DMA时钟的要求,则需要插入等待周期,从而延长整个DMA周期;使用压缩时序可以缩短DMA周期;如果存储器数据块首地址低8位为“0”,前256个字节内存地址的高8位相同,它们传送时只需要发送一次高8位地址,后面255个数据的DMA周期达到最小;如果进行存储器之间数据传输,每个字节的传输需要二个DMA周期。

习题九1.A/D和D/A转换在微机应用中分别起什么作用?计算机加工、处理的信号可以分为数字量(Digit)和模拟量(Analog)两种类型。现代计算机内部都采用二进制表示的数字量进行信号的输入、存储、传输、加工与输出。为了使用计算机对模拟量进行采集、加工和输出,需要把模拟量转换成便于数字计算机存储和加工的数字量(A/D转换),或者把数字量转换成模拟量(D/A转换)。因此,D/A与A/D转换是计算机用于多媒体、工业控制等领域的一项重要技术。2.怎样将D/A转换器连接到微型计算机?D/A转换器将数字量转换成模拟量输出。为了保存由计算机送来的数字信号,通常需要配置一个“数据寄存器”,向D/A转换器提供稳定的数字信号。D/A转换芯片输出的模拟信号功率一般比较小,为了能够驱动执行机构工作,D/A转换器的输出一般都要连接到运算放大器进行功率放大。3.修改图9-5,将DAC0832的两级锁存合为一级使用,画出连接图,并编写输出三角波和锯齿波的程序。为了将DAC0832的二级缓冲锁存器合为一级使用,可以将它的第二级置为“直通”,也就是把WR2和XFER接地,用第一级的WR1和CS对输入进行控制,如下图。DAC0832Vref2RD7-D0D7-D0Vref地址2RPORT译CSRfb码M/IO器Iout1-RXFER-WR2Iout2++VoutIOWWR1+5VILE模拟地输出三角波的程序段如下:S0:MOVAL,0;AL中置初值0,输出三角波的上升段S1:CALLOUTPUT;调用输出子程序,输出一个值INCAL;产生上升段下一个值JNZS1;上升段未结束,继续输出DECAL;恢复到最大值S2:CALLOUTPUT;输出三角波的下降段

DECAL;产生下降段下一个值JNZS2;下降段未结束,继续输出JMPS1;下降段结束,输出下一个三角波输出锯齿波的程序段如下:MOVAL,0J1:CALLOUTPUT;输出当前值INCAL;产生下一个输出值JMPJ1子程序“OUTPUT”为上面两段程序共用:OUTPUTPROCNEARMOVDX,PORT0;DAC0832端口地址OUTDX,ALPUSHAXMOVAX,N;延时的时间常数WT:DECAXJNZWT;延时POPAXRETOUTPUTENDP4.一个8位D/A转换器的满量程(对应于数字量255)为10V。分别确定模拟量2.0V和8.0V所对应的数字量。模拟量2.0V所对应的数字量为(2.0/10)×255=51模拟量8.0V所对应的数字量为(8.0/10)×255=2045.简述逐次逼近式A/D转换器的工作原理,并将它和∑-△A/D转换器进行比较。逐次逼近型(也称逐位比较式)A/D转换器主要由逐次逼近比较寄存器SAR,D/A转换器、比较器以及时序和控制逻辑等部分组成。它从SAR的最高位开始,逐位设定SAR寄存器中的数字量,经D/A转换得到电压VC,与待转换模拟电压Vx进行比较。通过比较,逐次确定各位的数码应是“1”还是“0”。转换结果能否准确逼近模拟信号,主要取决于SAR和D/A的位数。位数越多,越能准确逼近模拟量。∑-△型模数转换器是根据二次采样的差进行计算的,有很强的抗干扰能力,转换精度高,以串行方式输出数据。常用于高分辨率(常见为16、18、24位)的中、低频信号测量。当模拟量输入端接有多路开关时,通道切换后要等待足够长的时间,才能读取转换结果。6.若ADC输入模拟电压信号的最高频率为100KHZ,采样频率的下限是多少?完成一次A/D转换时间的上限是多少?香农定理告诉我们:采样频率一般要高于或至少等于输入信号最高频率的2倍。因此,

采样频率的下限应是200KHz。在200KHz采样频率下,完成一次A/D转换时间的上限是5μs。实际应用中,采样频率可以达到信号最高频率的4~8倍。如果采用400KHz的采样频率,完成一次A/D转换时间的上限是2.5μs。7.在使用A/D和D/A转换器的系统中,地线连接时应注意什么?模拟信号很容易受到电源和数字信号的干扰引起波动。为提高输出的稳定性,减少误差,模拟信号部分必须采用高精度基准电源VREF和独立的地线。所以,要把数字地和模拟地分开。模拟地是模拟信号及基准电源的参考地,其余信号的参考地,包括工作电源地,数据、地址、控制等对应的“地”都是数字地。连接时,先所有的模拟地连接在一起,把所有的数字地连接在一起,然后在一个点上(注意:不是两个或更多)把模拟地和数字地连接起来。8.怎样用一个AD芯片测量多路信息?模拟量多于一个时,可以使用多路模拟开关,轮流接通其中的一路进行转换,使多个模拟信号共用一个ADC进行A/D转换。9.一台工控PC有两块818卡,基地址分别为BASE1,BASE2,试编制采样24路(一块卡16路,一块卡8路)模拟量的C语言程序。#include“dos.h”#defineN24/*采样点数*/#defineBASE10x300#defineBASE20x310#defineINTERRUPT0x1c/*定时中断类型号*/staticunsignedad,tad[N],tt[N][16];voidfarhandler();/*函数handler()声明*/voidAD818(int);/*函数AD818()声明*/void(interruptfar*oldhandler)();/*定义oldhandler为指向中断服务程序的指针*/…………..main(){oldhander=getvect(INTERRUPT);/*读出原1CH中断向量*/setvect(INTERRUPT,handler);/*把新的1CH中断向量写入向量表*/…………..}voidAD818(intscan)/*函数AD818从AD818卡采集一次数据*/{intlbit,hbit,it=0,status,base,ch;/*采集结果置入全局变量ad中*/base=(scan<=15)?BASE1:BASE2;/*根据点号确定所在采集卡的基地址*/ch=scan%16;/*计算该点在本采集卡上的通道号*/outportb(base+2,ch);/*向AD818输出通道号*/outportb(base+1,0);/*AD输入量程控制*/

outportb(base+9,0);/*不使用中断或DMA*/outportb(base+0,0);/*启动AD转换*/do{it=it+1;status=inportb(base+8)&128;/*读出AD状态寄存器,查询EOC,等待AD转换完成*/}while(status!=0&&it<=10000);lbit=inportb(base+0)&240;/*读入低8位,清除其中无效的最低4位*/hbit=inportb(base+1);/*读入高8位*/if(it<=10000)ad=hbit*16+lbit/16;/*采集正常,拼接二段数据*/elsead=0;/*采集数据超时,818卡有故障*/}voidinterruptfarhandler()/*55ms定时中断服务程序,采集每个点的数据*/{intisp,s,i;for(isp=0;isp<=N-1;isp++){AD818(isp);/*采集一个模拟量,存入ad*/for(i=0,s=0;i<=14;i++){tt[isp][i]=tt[isp][i+1];/*移动队列中的数据,以便装入新的数据*/s=s+tt[isp][i];}/*求前15个数据的累加和*/tt[isp][15]=ad;s=s+ad;/*新数据进队列,求出16个数据的累加和*/tad[isp]=s/16;/*求出16个数据的平均值*/}oldhandler();/*进入原1CH中断服务程序,此后返回断点*/}

习题十1.查找相关资料,用列表方式给出8088,8086,……直到P4各代微处理器的地址、数据线引脚数量,并推算出各自的内存寻址空间。处理器数据线地址线内存寻址空间80888201MB808616201MB80286162416MB80386/48632324GBPentium64324GBPentium2~4643664GB2.什么是MMX指令?它有什么特点?MMX指令是“多媒体扩展指令”的英文简称,它采用SIMD(单指令流多数据流)技术,使得处理器在一条指令中对多个数据进行处理,提高了对多媒体数据的处理能力。3.什么叫动态执行?使用动态执行技术会带来什么好处?动态执行是通过预测指令流和数据流,调整指令的执行顺序,最大地发挥CPU内部各部件的功效,提高系统执行指令的速度。动态执行主要采用了:多路分支预测:利用转移预测技术允许程序几个分支流同时在处理器内执行;数据流分析:通过分析指令数据的相关性,把指令进行优化排序后执行,充分利用处理器内部资源;推测执行:根据各推测最终的正确性,对多个分支的运行结果进行取舍。4.32位微处理器有哪几种工作方式?各有什么特点?32位微处理器有4种不同的工作方式:实地址方式、保护方式、虚拟8086方式、系统管理方式。实地址方式:实地址方式使用16位80x86处理器的寻址方式(使用20位地址寻址1MB空间)、存储器管理和中断管理。可以使用32位寄存器,使用特权级0,可以执行大多数指令。保护方式:保护方式是32位微处理器的基本工作方式。它使用32位地址寻址4GB的实存空间,通过虚拟存储管理、用户优先级管理、I/O管理等技术,扩大可使用的存储空间,对操作系统和用户程序进行隔离和保护。虚拟8086方式:虚拟8086方式是保护模式下为任务提供的的8086工作环境。每个任务使用16位地址寻址1MB的内存空间,以最低特权级运行,不能使用特权指令。系统管理方式:系统管理模式主要用于电源管理,可以使处理器和外围设备部件进入“休

眠”状态,在有键盘按下或鼠标移动时“唤醒”系统,使之继续工作。利用SMM可以实现软件关机。5.叙述XT总线与ISA总线的异同之处。XT总线可以看作是ISA总线的一个“子集”,它包括8位数据线,20根地址线,使用与CPU相同的4.77MHz的时钟信号。ISA总线在XT总线的基础上,把数据线扩展到16根,地址线扩展到24根,使用独立于CPU的8MHz时钟信号,中断和DMA通道数目都有所增加。ISA总线插槽由8位的XT总线插槽和ISA总线扩展插槽两部分组成。6.什么叫分级总线?使用分级总线有什么优点?所谓分级总线是指系统中存在多组总线,每组总线可以有不同的数据线宽度、数据传输速率和不同的信号传输协议。系统内的设备按照它们对传输速率、数据吞吐量的不同要求合理地连接在不同的总线上。不同总线之间通过“桥”电路进行连接。使用分级总线可以使各种设备的数据传输要求得到最大程度的满足,同时使整个系统的数据吞吐量和效能达到最大化。7.简述‚两个中心‛结构与‚南北桥‛结构的区别,同时说明‚两个中心‛结构的优越之处。“南北桥”结构和“中心结构”都支持多级总线的系统结构。它们的主要区别在于,南桥芯片连接的所有高速外设都要通过PCI总线与处理器相连接,而“中心结构”里所有连接IO设备的总线(PCI,ISA,USB……)都通过IO控制中心(ICH)与中心高速接口直接连接,从而缓解了PCI总线数据交换的拥挤程度。相比较而言,“中心结构”对信息流的路径分配更为合理。8.CPU←→Cache,Cache←→主存,主存←→辅存之间的数据传输各有什么特点?为什么?请分析原因。CPU与Cache之间数据传输的主要特点是:高速:Cache以与CPU相同或接近的速度工作;不确定:CPU对Cache的访问可能因“命中”而成功,也可能以“失靶”而失败。Cache与主存之间数据传输的主要特征是:数据传输以“页”为单位,使用“成组传输方式(突发总线方式)”进行。导致上述特点的原因是,这一层次以“高速”为追求的目标,利用了程序、数据的“局部性”原理。主存与辅存之间的数据传输以“数据块/扇区”为单位,通常以DMA方式进行。导致上述特点的原因是,这一层次以“大容量”、“低价格”为追求的目标,辅存大容量、“粗粒度”的结构特点正好能够满足对上述目标的要求。系统对不同层次的数据传输有着不同的要求,因而设置了不同的软硬件结构,最终导致了传输方式上的差异。

9.什么叫‚相联存储映像表‛?说明它的结构和用途。相联存储映像表是Cache内纪录Cache中各页在主存的位置和其他信息的表格,由各页的“标记(Tag)”,“状态”和“LRU位”组成。“标记(Tag)”记录了该页在主存中的位置,供CPU访问时进行匹配查找使用。“状态”和“LRU位”用于Cache页的替换操作。10.为什么要进行Cache和主存的‚映像‛?有哪几种相联映像的方法?比较各自的利弊。Cache和主存的“映像”是主存页调入Cache的“规则”,为了提高CPU在Cache中查找信息的速度,这种“规则”是必须的。常见相联映像的方法有三种:全相联映像法:内存页可以调入Cache的任何一页,规则简单,页冲突的可能性最小,查找所需工作量最大。直接映像法:每一个内存页只能调入Cache中相同页号的一个页,规则简单,查找方便,块冲突的可能性大。组相联映像法:每一个内存页可以与Cache中一个组内的若干个页面相对应,规则稍复杂,查找工作量中等,块冲突的可能性中等。11.什么叫‚突发总线周期‛?它有什么优点?“突发总线周期”也称为“成组传送方式”,总线主设备在发送一个主存地址之后,通过连续的多个周期,传输(读/写)多个地址相连的存储单元的数据。这种方式省去了多次发送地址、多次申请总线和多次相互联络的过程,因此可以获得很高的数据传输速率。12.逻辑地址是怎样转换成线性地址的?简要叙述转换过程。实地址方式下没有“线性地址”。保护模式下,逻辑地址由“段号”和“段内地址”两部分组成。使用“段号”查找“段描述符表”,可以获得该段的起始地址,与“段内地址”相加,就得到了对应的“线性地址”。13.线性地址是怎样转换成物理地址的?简要叙述转换过程。“线性地址”由处于高位的“页组号”、处于中间的“页号”和处于低位的“页内地址”三部分组成。用“页组号”查找“页组表”,得到“页表”的起始地址;用“页号”查找该“页表”,得到该页的起始地址;页起始地址加上“页内地址”就得到了它对应的物理地址。14.请分析使用虚拟存储管理带来的利弊。虚拟存储管理把辅存的一部分用作“虚拟”的主存,扩大了操作系统可分配,程序员可利用的存储空间,便于实现任务之间的隔离和保护,有效地支持了“多任务”运行环境的实现。它还可以有效地克服“内存碎片”问题,简化了存储管理。但是,实现虚拟存储后,每次访问主存都需要进行两次地址的转换,增加了系统的复杂性,增加了系统的硬件成本,降低了访问主存的速度,而且,由于系统复杂程度的增加,系统的可靠性也会受到影响。

15.32位微处理器实施保护机制的目的是什么?有哪些主要措施?32位微处理器实施保护机制的根本目的在于增加在“多任务”运行环境下系统的可靠性,使得任务之间、任务和操作系统之间实现隔离和保护。为了实现隔离和保护,采取了以下几项措施:为任务和资源设定一个“优先级”,优先级较低的任务不能访问优先级较高的资源,不能调用优先级较高的程序模块。使用虚拟内存管理机制,使得任务和任务、任务和操作系统所使用的存储空间相互隔离,从而保证每个任务的正常运行不受其它任务的影响,一个任务的故障不影响整个系统的正常运行。16.说明操作系统在保护模式下启动一个任务的过程。一个任务用JMP或CALL指令启动一个新的任务时,处理器将当前任务的所有通用寄存器、所有段寄存器中的选择子、EFLAGS、EIP存入该任务自身的TSS,然后将新任务的选择子、描述符装入TR寄存器,并且将对应TSS段中所保存的通用寄存器、段寄存器、EFLAGS、EIP副本装入处理器对应的寄存器中。在CS:EIP的控制下,一个新的任务开始执行。用JMP、CALL指令调用同一个任务中其他程序段时,指令中的“段选择子”及其描述符被存入CS寄存器,“偏移地址”进入EIP,于是,目标程序被执行。对于CALL指令,原来程序的返回信息“CS:EIP”被压入堆栈,和16位微处理器中十分相似。中断和异常也会导致任务的转换。17.32位微处理器如何实施对I/O过程的管理?保护方式下对I/O过程的管理主要有两项措施:任务状态段TSS中有一个最多64Kbits组成的“I/O允许位图(IOM)”,它的每一位对应一个I/O端口,为0表示该端口允许这个用户进行I/O操作。处理器首先检查存放在CS中的当前任务的CPL(当前任务优先级),如果CPL的特权级高于或等于EFLAGS中由IOPL规定的特权级,I/O操作不会受限制,否则将进一步检查IOM,对IOM为1的端口进行操作将产生保护异常;对于运行在虚拟8086方式的任务,用IOM来控制对I/O端口进行访问,对位图对应位为1的端口进行访问将产生保护异常。另一种办法是:在IOM中封锁对所有端口的访问,当前任务一旦执行I/O指令,立即产生保护异常,进入由操作系统设置的“异常处理程序”,在操作系统的控制下进行间接的“I/O操作”。18.简要叙述保护方式与实地址方式下的中断管理方法的区别。在实地址方式下,32位80X86微处理器采用与16位80X86相同的中断管理机制,用1KB大小的“中断向量表”存储各中断服务程序入口地址,这些“中断向量”按照“中断类型”的顺序存放。中断向量表存放在地址0000:0000开始的主存中。保护方式下用“中断描述符表”来指出各中断处理程序的入口地址,每一个中断类型对

应一个“中断门”或“陷阱门”描述符。中断描述符表可以放在内存的任何位置,表的首地址存放在IDTR寄存器中。保护模式下中断响应的过程与实地址方式基本相同,但是可以用中断机制进行任务的切换。19.什么叫‚串行中断‛?它有什么优点?串行中断用一根SERIRQ来传递中断请求信号。SERIRQ信号线上的信息组织成“包”,用PCI的时钟信号对“包”内的信号进行同步。所有支持串行中断的设备都可以用一个三态门连接到这根线上发送各自的中断请求信号。使用串行中断减少了中断请求的引脚数,可以不受中断请求引脚的限制灵活地扩充中断请求数目。20.什么叫‚APIC‛中断?它有什么用途?APIC是“高级可编程中断控制子系统”的缩写,用于解决多处理器环境下处理器之间的联络、任务分配和中断处理。

习题十一1.按功能分,计算机外围设备可分成哪几类?答:计算机外部设备按照它们的功能,一般可分为三类:供用户进行输入/输出的设备,如键盘、鼠标、显示器等,它们也称为“人机交互设备”;外存储设备,软盘、硬盘、光盘驱动器是典型的外存储设备;专用的其它设备,如数据采集设备、视频采集设备等。2.何谓编码键盘和非编码键盘?答:非编码键盘:由CPU对键盘各行、各列的状态进行扫描,根据扫描结果,用某种算法计算或查表得到按键的编码。CPU效率低,主要用于小型应用系统。编码键盘:由专用控制器/控制电路对键盘进行扫描,产生按键所对应的编码供CPU读取。这种键盘结构稍复杂,但使用方便。3.请说明101键盘接口电路的基本组成原理。答:参考教材相关内容(图11-1),101键盘接口电路由8048专用单片处理芯片,键盘开关矩阵电路,双向缓冲门电路组成。有规律的内部计数信号通过数据线DB0~DB6,送到键盘矩阵的行列译码器,实现对键盘开关矩阵的行列扫描。有键按下时,通过KEYDEP信号通知单片机。8048扫描程序根据当前计数值,分析确定按键的行、列位置,形成键盘扫描码。4.鼠标常用接口有哪几种类型?简述光机鼠标的工作原理。答:目前PC上常用的鼠标接口有3种,第一种是最常用的直径8mm的6芯PS/2鼠标接口,第二种是9芯D型插座(使用RS-232串行接口),另外是较新型的USB鼠标接口。光机鼠标的工作原理:鼠标内置了2个滚轴,X方向滚轴和Y方向滚轴。这2个滚轴都与一个可以滚动的橡胶球接触,并随着橡胶球滚动一起转动。X,Y滚轴上装有带孔的译码轮,它的转动会阻断或导通LED发出的光线,在光敏晶体管上产生表示位移的脉冲。通过脉冲编码确定光标移动的方向和距离。5.论述打印机接口的主要通信连接信号。答:打印机接口的主要控制信号(输出)有:STROBE:数据选通,低电平有效。数据在它的配合下送入打印机。AUTO_FD:自动换行,高电平有效。有效时打印机每次回车后自动换行。INIT:初始化信号,低电平有效。有效时,打印机被复位。SEL:联机控制位,高电平有效。有效时打印机才能与接口连通。

主要状态信号(输入)有:BUSY:忙信号,高电平表示打印机忙。有四种情况:正在输入数据、正在打印操作、在脱机状态、打印机出错。ACK:确认,低电平有效。有效时表示打印机已经接收完毕接口送来的一个数据。PE:纸尽信号,高电平有效。有效时表示打印机缺纸。SLCTIN:选择信号,高电平有效。有效时表示打印机处于联机状态。ERROR:出错信号,低电平有效。有效时表示打印机出错。6.分别叙述IDE和EIDE磁盘接口的技术特性。答:IDE磁盘接口的技术特性:IDE接口在ST506的基础上进行改进而成,它把控制器集成到驱动器内。消除驱动器和控制器之间的数据丢失问题,提高数据传输的可靠性。从驱动器中引出的信号线已不是控制器和驱动器之间的接口信号线,而是通过简单处理后可与主系统连接的信号线。IDE采用了40线单组电缆连接,除了对系统总线上的信号做必要的处理之外,其余信号基本上是原封不动地送往硬盘驱动器,IDE实际上已经是系统级的接口。EIDE磁盘接口的技术特性:与IDE相比,EDIE有以下几个方面的特点:支持大容量的硬盘(>540MB);EIDE允许连接更多的设备。通常提供两个插座,称为主插座和辅插座,每个插座可连接主、从两个设备,一共可连接4个设备;EIDE具有更高的数据传输速率。标准EIDE驱动器的最大突发数据传输率可达16MB/S,而原有的IDE驱动器的最大突发数据传输率仅为3MB/S;EIDE支持三种硬盘工作模式:普通模式(Normal)、逻辑块寻址模式(LBA)、大硬盘模式(LAG)。7.硬盘的主要技术指标包括哪些?答:硬盘的主要技术指标包括:硬盘容量:硬盘能够储存的信息的总量。传输速率:单位时间内传输的信息数量。影响传输速率的因素有电机转速、存储密度、Cache容量、接口方式等。平均寻道时间:磁头寻找目标磁道的时间,影响磁盘的工作速度。转速:IDE接口硬盘工作时主轴和碟片转速多为5400rpm和7200rpm两种。转速越高,硬盘的传输速率越高;除了上面主要的指标之外,下面几项指标也影响硬盘的性能。单碟容量:硬盘一般由四到五张碟片组成。单张碟片的容量越大,硬盘的总容量随之增大,数据读写速度也越快;Cache:硬盘中Cache的容量越大,硬盘的实际传输率就越大。硬盘采用的Cache现多为

512KB和2MB两种。磁头类型:目前有两种类型的磁头:磁阻磁头MR(MagnetoResistiveheads)和巨磁组磁头GMR(GiantMagnetoResistiveheads)。MR和GMR磁头通过磁阻的变化去感应信号的幅度,具有高灵敏度,高可靠性的优点;8.简述显示器技术性能指标和显卡的种类。答:显示器有以下主要技术性能指标:尺寸:通常指的是显像管的对角尺寸(英寸),实际显示面积小于标称尺寸;点距:相同颜色两个相邻的磷光体间的距离。点距越小,显示出来的图像越细腻,目前大多数显示器的点距是0.28mmn和0.25mm。刷新频率:是显示器每秒屏幕刷新的次数,刷新频率越高,图像显示就越稳定。在不同的分辨率下,对应的刷新频率可能有所不同。带宽:带宽是显示器每秒扫描像素的点数,常见的是几十兆,高性能显示器的带宽在100M以上。分辨率:指水平方向和垂直方向上最大像素个数.用水平方向像素数×垂直方向像素数来表示。显像管的形状:主要有球面、平面直角和纯平几种,以平面直角和纯平最为常见;扫描方式:有逐行扫描和隔行扫描两种,目前都为逐行扫描方式;显卡的种类:MDA单色显示卡:它只有字符方式,无图形输出能力;CGA彩色图形显示卡:它支持字符、图形两种方式。但分辨率不高,颜色种类较少;EGA增强型图形显示卡:其字符、图形功能比CGA卡有较大提高,显示分辨率也较高;VGA视频图形阵列显示卡:标准分辨率为640×480,16种颜色。VGA卡兼容了上述各种显示卡的显示模式,支持更高的分辨率和更多的颜色种类。SVGA(超级VGA)显示卡:SVGA是一种比VGA更强的显示标准。SVGA的标准模式是800×600,新型显示器分辨率可达1280×1024、1600×1200等。9.试计算1024×768分辨率、24位彩色所需的显存为多少?答:所需的显存大小为:24/8×1024×768=2,359,296(Byte)=2.25MB10.何谓AGP显示总线接口?AGP4X的数据传输速率是多少?答:AGP显示总线接口(加速图形接口)是新一代局部图形总线技术,为任务繁重的图形加速卡提供了一条专用高速通道。采用与外频相同的时钟频率进行数据传输时,AGP总线的数据传输速率为266MB/S,是PCI总线数据传输率的两倍。借助如此高的传输率,我们可以使一些原本只能在显存中进行的函数运算扩展到主存中。AGP有两种模式:DMA模式和Execute模式。DMA模式适用于从系统内存到图形内存之间的大批量数据传输。系统内存中的数据不能被图形加速器直接调用,只有调入图形内存才能被图形加速芯片所寻址。在Execute模式中,加速芯片将图形内存与系统内存看作一体,

通过一种叫做图形地址再映象的机制,使加速芯片可直接对系统内存寻址,减轻局部图形内存的压力。AGP4X的数据传输速率是1064MB/S(=266MB/S×4)。11.简述声卡的工作原理,声音的采集和还原采用了什么技术?衡量音质好坏的技术指标有哪些?答:声卡主要由总线接口控制芯片、混音控制芯片、数字信号处理器(DSP)、A/D及D/A转换器、高级信号接口等组成。输入到声卡的声音信号首先由模数转换器ADC把模拟信号转换成数字信号,这个过程称为“采样”。然后,DSP(数字信号处理器)将来自ADC的信号加以处理,对输入的数字声音用PCM、DPCM或ADPCM方式进行编码和压缩,并形成WAV格式文件送入计算机磁盘存储。对计算机内以文件形式存放的声音输出(回放)时,磁盘中的WAV文件首先送入DSP芯片,经解码后变成数字声音信号送至D/A转换部分。数模转换器DAC把数字信号还原为模拟信号,驱动扬声器单元发声。音乐合成器用来播放MIDI音乐文件。播放时,MIDI信息从文件中读出,经MIDI接口送至合成器。合成器将这些信息转换成乐器的音阶、音色、持续时间等,经处理后变成声音信号输出。技术指标有:采样频率:它决定了声音采集的精度,足够的采样频率能保证不丢失有效信号。采样频率越高,采集得到的信号越能精确地保存原信号的特征;采样的量化值:它决定了每个采样点的采样精度,量化值越大,所记录声音的变化程度就越细腻。常用的几种采样频率与量化值的组合:11KHz/8bitMono电话音质;22KHz/8bitStereo调幅广播水平;22KHz/16bitStereo音乐磁带的音质水平;44KHz/16bitStereo音乐CD或调频广播音质水平。12.IEEE1394串行总线的通信方式有哪两种?为什么说1394接口比较适合数字视频的传输?答:IEEE1394总线上的通讯有异步和同步两种模式。对于异步传输,数据发送方和接收方互换地址,然后进行数据传输。接收方收到数据包后,向发送方传回确认信息。接收方没有收到数据包,则启动错误修复机制。对于同步传输,发送方首先要获得一个特定带宽的数据通道,然后将标志接收方的通道标识(ID)附加在所要传输的数据中一起发送。接收方对数据流进行检测,对具有特定ID信号的数据时进行接收。同步数据传输模式的优先级高于异步传输模式。

由于1394的同步传输方式传输速率高,优先级高,使用CPU资源少,所以特别适合于传输数字视频。13.USB通用串行总线和IEEE串行1394总线有哪些不同?答:它们的主要区别是:(1)USB要求CPU来控制数据的传输,有一定的CPU占用率,IEEE1394不需要CPU控制,CPU的占用率极低。(2)USB只支持异步传输,IEEE1394不仅支持异步数据传输也支持同步数据传输。(3)USB需要使用集线器连接各设备。IEEE1394不需要集线器(HUB)就可连接63台设备。(4)另外,IEEE1394的数据传输速率总体上高于USB。

习题十二1.总线的指标有哪几项?总线标准和总线产品哪一个先产生?(1)总线宽度:总线宽度是可以同时传输的数据位数,位数越多,一次传输的信息就越多。(2)总线频率:总线通常都有一个基本时钟,总线上其它信号都以这个时钟为基准,这个时钟的频率也就是总线工作的最高频率。总线频率越高,单位时间内传输的数据量就越大。(3)单个数据传输周期数:传输方式的不同,使得每个数据传输所用的时钟周期数不同。单个数据传输周期数越少,传输率越高。此外,总线的仲裁方式,容错性能,是否支持突发成组传输,也反映了总线的性能。总线标准的产生有多种形式。有的总线产品推出后得到广泛的认同,随后成为事实上的工业标准,这个产品所采用的技术规范最终成为标准,标准产生在产品之后。有的技术问题得到较多的关注,由标准化组织或者相关集团发起,制定了相应的标准。这时,产品的出现晚于标准的制定。2.ISA卡设计时如何解决资源冲突问题?ISA的I/O空间仅有100H~3FFH的768个地址可供使用,其中不少端口已分配给“常规”的设备使用,新设计I/O扩充卡的端口地址不能与它们冲突。另外,扩充卡之间使用的地址也不能发生冲突。为解决这个矛盾,ISA卡上一般都设有一组开关(switch),用户可以通过设定这组开关来设置这块ISA所占用的I/O起始地址,使它位于所使用计算机I/O的空闲位置,从而避免发生冲突。3.ISA总线需要进行总线仲裁吗?为什么?ISA总线是一个简单的多主控总线,需要使用总线的“主设备”是CPU和最多7个使用DMA传送的设备。当CPU以外的一个或多个设备需要使用总线时,需要进行“总线仲裁”。对于使用DMA请求使用总线的设备来说,“仲裁”要分两次进行:①DMA请求信号送到8237,由8237进行第一次“仲裁”;②8237的请求信号发送到CPU,在一个总线周期结束时释放总线。4.若有两块818ISA卡BASE1=0x0250,BASE2=0x0330,switch分别应如何设置?BASE1=0x250:swith1,4,6=offswith2,3,5=onBASE2=0x320:swith1,2,5=offswith3,4,6=on5.PCI总线怎样的信号组合启动一个总线的访问周期,又怎样结束一个访问周期?它的AD0~AD31同CPU的同名引脚有何不同?主设备获得总线使用权后,将FRAME#置为有效,在AD0~31上发出地址信号,C/BE#上发出总线命令,一次总线访问周期开始。

主设备在发出最后一组数据读写的启动信号之后,将FRAME#信号置为无效,表示数据传输即将结束。在最后一项数据传输后,主设备撤销IRDY信号,从设备撤销TRDY#和DEVSEL#信号,一次PCI总线传输结束。PCI总线信号独立于CPU,使用独立于CPU的时钟信号。对于PCI总线来说,CPU是它所连接的众多设备中的一个。PCI总线的AD0~31是地址和数据分时复用信号,它们与CPU同名引脚传输的信号类型相同,但是并不等同。CPU对PCI总线上设备进行访问时,CPU发出的地址经Host/PCI桥缓冲,按照PCI的时序定时后由桥电路向PCI总线“转发”。DMA传输时,PCI总线上的AD0~31来自DMA控制器而不是来自CPU。6.一块PCI卡上最多可以实现多少路中断信号?由于PCI总线上只有4条中断请求线,因而一块PCI卡最多可以实现4路中断请求。说明:①对于单项功能的PCI卡,只能使用INTA#请求中断;对于对功能PCI卡,可以使用其它的三根中断请求引脚。②PCI总线允许“共享”中断请求信号线,这是与以前有较大区别的。例如,有两块PCI卡插在PCI总线上,按照规定,他们都使用同一个INTA#申请中断。在“中断描述符表”上,中断服务的入口可能是设备甲,或者是设备乙,现假设为设备甲。如果设备乙申请中断,那么,首先会进入设备甲的中断服务程序。该程序通过查询状态,发现自己并没有申请中断,于是发出相应信息后返回。此后,由操作系统调度进入设备乙的中断服务程序(参见习题11第8题答案)。③PCI总线上的中断请求进入ICH芯片后,与“SIO”芯片送来的“串行中断”(由传统设备键盘、鼠标、串口、并口、软驱发出,通过L/F总线传送到ICH芯片)一起,被送往ICH芯片内的“中断申请信号路由器”。可以通过程序来设置每一个中断请求使用的实际的中断请求引脚(除少数已集成在CPU内,中断类型固定的申请以外),最终由“路由器”产生12个中断申请信号,送到芯片内两个级联的8259中断控制逻辑。主片8259产生的中断请求最终由ICH的INTR引脚送往CPU。7.在PCI卡配置空间中,基地址寄存器的作用是什么?一个PCI设备最少可申请多少地址空间?最少可申请多少I/O空间?PCI总线上的设备采用“即插即用”的方法,所有设备使用的存储空间和IO空间的具体位置事先是不确定的,需要在系统初始化时通过“配置”过程来确定。PCI卡上的基地址寄存器有两个方面的作用:(1)寄存器的最低的几位记录申请所需空间的类型(存储器空间/IO空间)、空间的大小等信息(寄存器的这几位是只读的)。(2)寄存器的高位用来纪录操作系统分配给它的存储空间/IO空间的起始地址(寄存器的这几位是部分可写的)。由于有6个基地址寄存器,PCI设备最多可以申请6段地址空间。对于申请存储空间的基地址寄存器,它的第0~3位是只读位,第4~31位用来表示申请地址空间的大小,因而一个PCI设备申请地址空间最少是16个byte。对于申请I/O空间的基

地址寄存器,它的第0~1位是只读位,第2~31位用来表示申请地址空间的大小,因而申请I/O地址空间最少是4个byte。例如,某PCI设备申请1MB的存储空间,它的基地址寄存器位0~位19均为只读。其中:位0固定为0,表示申请存储器空间;位1~2表示“映射”的类型,如果基地址寄存器为32位,可以“映射”到32位地址空间的任何位置,这两位可以固定为“00”;其余位均固定为0。系统进行配置操作时,向该寄存器写入32位全“1”,然后读出该寄存器的内容。由于低20位均为只读位,所以实际读出的内容为高位12个“1”和低位20个“0”。其中位0~位2表示空间类型和“映射”类型,其它的“0”(位4~位19)表示了申请空间的大小。随后,系统根据各设备的请求进行空间的统一分配,将分配给该设备的存储空间首地址写入该基地址寄存器。对于1MB的空间而言,它首地址的低20位应为0,它的高12位反映了实际的起始地址。基地址寄存器的高12位正好能容纳这12位“有效”的起始地址。8.USB主机怎样了解USB设备的接入?集线器的D+和D-线上各有一个15KΩ的下拉电阻,没有USB设备连上时,D+和D-线都为低电平。全速和高速设备在D+线上有一个1.5kΩ的上拉电阻,而低速设备在D-线上有一个1.5kΩ的上拉电阻。当集线器有USB设备连接上时,D+和D-线中会有一根变成高电平。集线器通过监视D+和D-线来判断有哪一种速度的设备连上了USB总线。集线器发现D+线变成高电平时,再次向设备发出询问,高速设备会响应这个询问,而全速设备则不会响应。这样集线器就知道所连接上的USB设备的速度。反过来,对高速USB设备来讲,如果发现集线器的这个询问,就知道它所连接的集线器是支持高速的,否则集线器是不支持高速的。到此,集线器和设备都知道了对方的速度,接下来的通讯以双方所共同支持的最高速度进行。9.一台微机有5台USB设备,另一台微机有10台USB设备,各需用四端口的集线器几个?画出它们的结构图。5台USB设备,需用四端口的集线器1根集线器根集线器个(不包括根集线器)。HUBHUBHUB10台USB设备,需用四端口的集线器3个(不包括根集线器)。HUB它们的连接如右图所示。连接5台设备连接10台设备10.用8086汇编程序读出(注意是32位)PCI设备所分配到的存储器首地址。MOVAH,0B1H;MOVAL,02H;MOVCX,设备ID值;

MOVDX,厂商ID值;MOVSI,0;索引号INT1AH;得到总线号(BH)、设备号(BL高5位)、功能号(BL低3位)JCERROR;错误时转ERRORPP:MOVAH,0B1H;MOVAL,09H;AL=09H,读取基址寄存器内容QQ:MOVDI,10H;第一个PCI基址寄存器地址INT1AH;ANDAH,AH;AH=0表示读取成功JNZERRORTESTECX,01;ECX末位=0,该寄存器存放存储空间首地址JZMMANDECX,0FFFFFFFCH;ECX末位=1,该寄存器存放I/O空间首地址(高30位)STCJMPDONEMM:ANDECX,0FFFFFFF0H;从基地址寄存器获取存储空间首地址(高28位)DONE:MOVEAX,ECX;说明:(1)读取PCI配置信息需要知道该PCI设备的设备ID值(置于CX中)和厂商ID值(置于DX中)。然后用AH=0B1H,AL=02H的INT1AH功能调用获得该PCI设备的总线号(BH),设备号(BL高5位)、功能号(BL低3位)。(2)一个PCI总线设备可以有6个基地址寄存器,本程序只读取了第一个基地址寄存器所存储的配置空间首地址。读取其他配置空间首地址可以重复使用从“PP”标号开始的程序,同时修改标号为“QQ”的指令中的PCI基地址寄存器地址。第二个基地址寄存器地址为14H,第3个为18H,……,以此类推。(3)如果基地址寄存器存放的是存储空间基地址,它的末位为0,高28位添加4个0就是操作系统分配给该设备的存储空间首地址(不讨论64位基地址的情况)。如果基地址寄存器存放的是I/O空间基地址,它的末位为1,高30位添加2个0就是操作系统分配给该设备的I/O空间首地址。(4)为了区分读出的是存储空间基地址还是I/O空间首地址,上述程序用CF加以区分:CF=0,读出的是存储空间基地址(在EAX中);CF=1,读出的是I/O空间基地址(在EAX中)。11.两台PCI设备之间可直接传输数据吗?两台USB设备之间呢?两台PCI设备之间可直接传输数据。由PCI主设备申请使用总线,获得总线使用权后用地址信号呼叫从设备,然后进行数据传输。两台USB设备之间不可直接传输数据。USB总线采用“主-从”方式进行通讯,每一

次数据传输必须由USB主机发起。这样,两台USB设备之间的数据传输必需通过USB主机间接进行。12.那些总线具有热插拔功能?对哪一类总线这个功能是必需具备的?USB总线和PCI总线都支持热插拔(HotPlugIn)。对于USB总线来说,热插拔功能是必需的。需要说明的是,目前一般PC机内的PCI总线设备不支持“热插拔”功能。实现该功能需要相应的软、硬件的支持。“热插拔”的PCI总线设备主要应用于某些通讯设备中。13.从硬件来讲,一个USB信息传输到微处理器需经过那几个环节?USB总线上的数据传输是一种“主-从式”的传输,所有的传输都由USB主机发起。一个USB信息传输到CPU需经过集线器、根集线器和控制器这几个环节。14.为什么PCI/ISA扩展桥必须对总线上的地址进行负向译码?地址在哪个范围内?PCI总线设备在接收到落在自己地址范围内的地址信号时,发出DEVSEL#信号进行应答。如果没有一个设备对主设备发出的地址作出响应,则由一个指定的设备对主设备的呼叫作出响应,这个设备称为负向译码设备。ISA总线与PCI总线有着不同的信号传输协议,ISA总线设备没有对主设备进行应答的功能。为了使PCI主设备与ISA总线从设备的数据传输能够正常进行,必须由PCI/ISA扩展桥充当ISA从设备的代理,进行负向译码,对PCI主设备的呼叫进行应答。由于ISA总线上的I/O设备仅对低10位的地址线进行译码,并且前256个地址已经分配给系统板上的I/O接口芯片,所以ISA的I/O空间在0100H~03FFH(十六进制)的768个地址之内。'

您可能关注的文档

- 《物联网技术与运用》选择判断题答案.doc

- 《特殊需要学生的融合教育》总论第一章练习题及答案.doc

- 《环境化学》(戴树桂 第二版)课后部分习题解答和重要知识点.doc

- 《环境化学》戴树桂(完整版)_课后习题答案.doc

- 《环境化学》戴树桂(第二版)_课后习题答案.doc

- 《环境化学》戴树桂(第二版)_课后习题答案.pdf

- 《环境化学》戴树桂(第二版)课后习题答案.doc

- 《现代企业管理学》习题答案.doc

- 《现代企划》课后习题答案.docx

- 《现代控制理论》刘豹著(第3版)课后习题答案(最完整版).pdf

- 《现代教育理论》学生网络习题答案.doc

- 《现代检测技术及仪表》第2版习题解答(孙传友编).doc

- 《现代检测技术及仪表》第2版习题解答.doc

- 《现代汉语》(增订四版)补充练习题答案(全).doc

- 《现代汉语》(增订四版)补充练习题答案(全).pdf

- 《现代汉语》(增订四版)课后练习答案.doc

- 《现代汉语》黄伯荣_-廖序东-上下册-课后习题答案.doc

- 《现代汉语》黄伯荣课后答案.doc