- 1.48 MB

- 2022-04-29 13:51:48 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

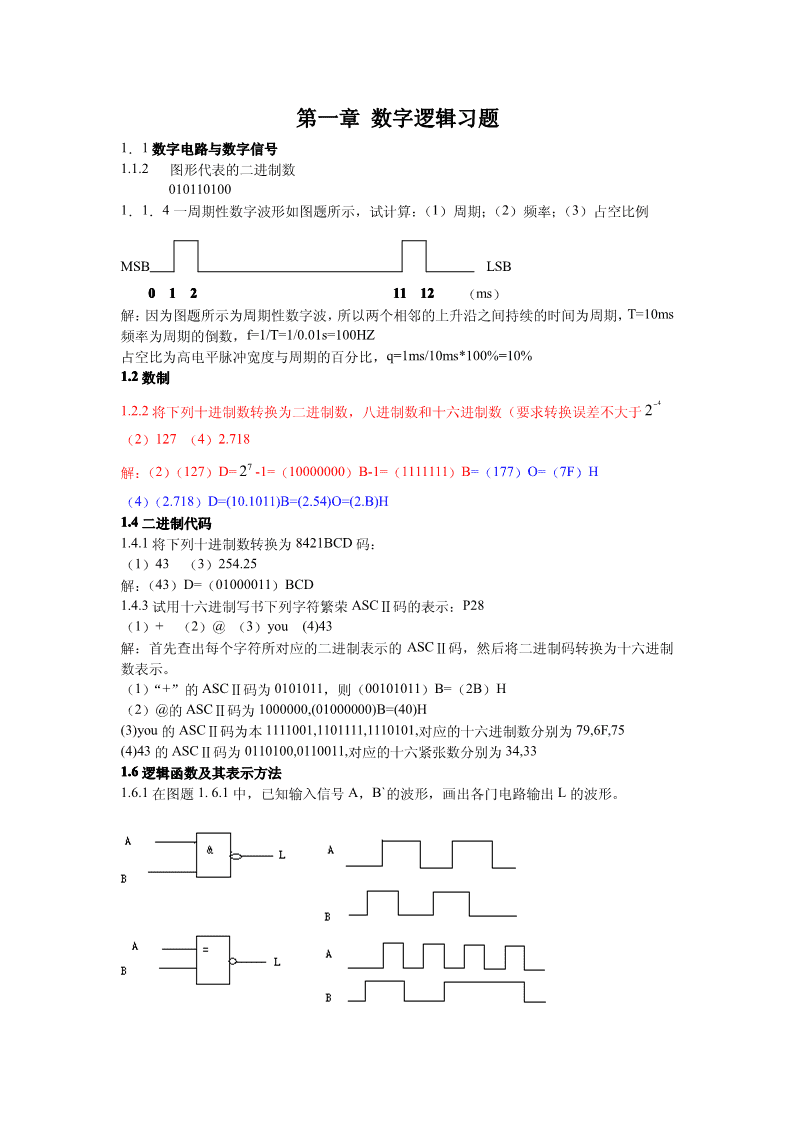

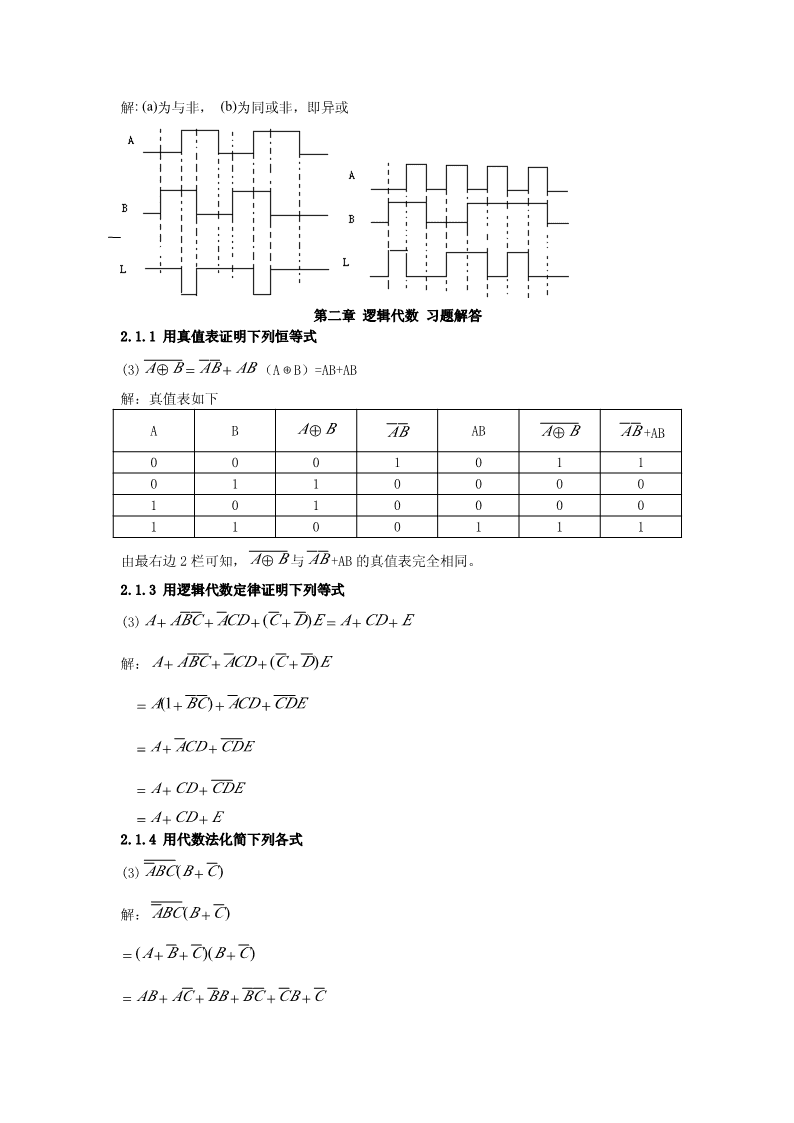

'第一章数字逻辑习题1.1数字电路与数字信号1.1.2图形代表的二进制数0101101001.1.4一周期性数字波形如图题所示,试计算:(1)周期;(2)频率;(3)占空比例MSBLSB0121112(ms)解:因为图题所示为周期性数字波,所以两个相邻的上升沿之间持续的时间为周期,T=10ms频率为周期的倒数,f=1/T=1/0.01s=100HZ占空比为高电平脉冲宽度与周期的百分比,q=1ms/10ms*100%=10%1.2数制−41.2.2将下列十进制数转换为二进制数,八进制数和十六进制数(要求转换误差不大于2(2)127(4)2.7187解:(2)(127)D=2-1=(10000000)B-1=(1111111)B=(177)O=(7F)H(4)(2.718)D=(10.1011)B=(2.54)O=(2.B)H1.4二进制代码1.4.1将下列十进制数转换为8421BCD码:(1)43(3)254.25解:(43)D=(01000011)BCD1.4.3试用十六进制写书下列字符繁荣ASCⅡ码的表示:P28(1)+(2)@(3)you(4)43解:首先查出每个字符所对应的二进制表示的ASCⅡ码,然后将二进制码转换为十六进制数表示。(1)“+”的ASCⅡ码为0101011,则(00101011)B=(2B)H(2)@的ASCⅡ码为1000000,(01000000)B=(40)H(3)you的ASCⅡ码为本1111001,1101111,1110101,对应的十六进制数分别为79,6F,75(4)43的ASCⅡ码为0110100,0110011,对应的十六紧张数分别为34,331.6逻辑函数及其表示方法1.6.1在图题1.6.1中,已知输入信号A,B`的波形,画出各门电路输出L的波形。

解:(a)为与非,(b)为同或非,即异或第二章逻辑代数习题解答2.1.1用真值表证明下列恒等式(3)A⊕B=AB+AB(A⊕B)=AB+AB解:真值表如下ABA⊕BABABA⊕BAB+AB0001011011000010100001100111由最右边2栏可知,A⊕B与AB+AB的真值表完全相同。2.1.3用逻辑代数定律证明下列等式(3)AABC++ACD+(C+DE)=ACDE++解:AABC++ACD+(C+DE)=A(1+BC)+ACDCDE+=A+ACDCDE+=ACDCDE++=ACDE++2.1.4用代数法化简下列各式(3)ABCBC(+)解:ABCBC(+)=(ABCBC++)(+)=AB+AC+BB+BC+CBC+

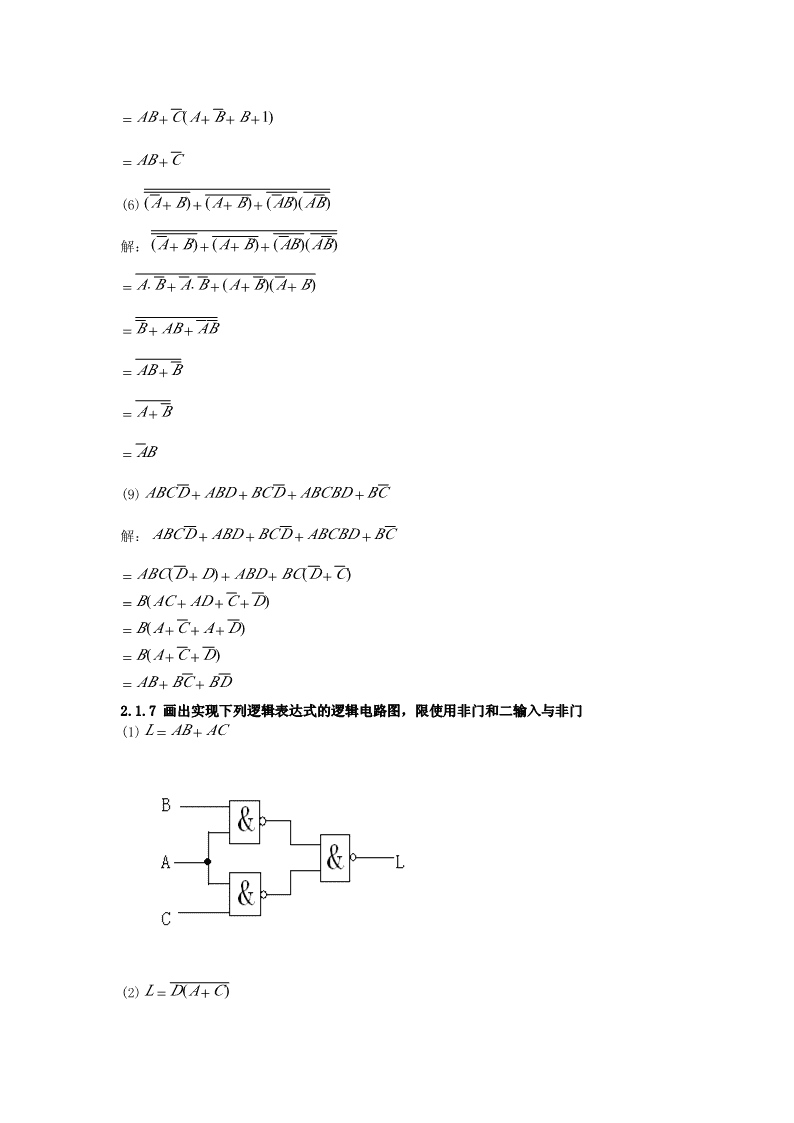

=ABCABB+(+++1)=ABC+(6)(AB+)(+AB+)(+ABAB)()解:(AB+)(+AB+)(+ABAB)()=AB⋅+AB⋅+(ABAB+)(+)=B+AB+AB=ABB+=AB+=AB(9)ABCD+ABD+BCD+ABCBD+BC解:ABCD+ABD+BCD+ABCBD+BC=ABCD(+D)+ABD+BCDC(+)=BAC(+ADC++D)=BAC(++AD+)=BAC(++D)=ABBC++BD2.1.7画出实现下列逻辑表达式的逻辑电路图,限使用非门和二输入与非门(1)L=AB+AC(2)L=DAC(+)

(3)L=(ABC+)(+D)2.2.2已知函数L(A,B,C,D)的卡诺图如图所示,试写出函数L的最简与或表达式解:LABCD(,,,)=BCD+BCD+BCD+ABD2.2.3用卡诺图化简下列个式(1)ABCD+ABCD+AB+AD+ABC

解:ABCD+ABCD+AB+AD+ABC=ABCD+ABCD+ABCCD(+)(+D)+ADBBCC(+)(+)+ABCD(+D)=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD(6)LABCD(,,,)=∑m(0,2,4,6,9,13)+∑d(1,3,5,7,11,15)解:L=AD+(7)LABCD(,,,)=∑m(0,13,14,15)+∑d(1,2,3,9,10,11)解:L=AD+AC+AB

2.2.4已知逻辑函数L=ABBCCA++,试用真值表,卡诺图和逻辑图(限用非门和与非门)表示解:1>由逻辑函数写出真值表ABCL000000110101011110011011110111102>由真值表画出卡诺图3>由卡诺图,得逻辑表达式L=ABBC++AC用摩根定理将与或化为与非表达式L=ABBC++AC=ABBCAC⋅⋅4>由已知函数的与非-与非表达式画出逻辑图第三章习题

3.1MOS逻辑门电路3.1.1根据表题3.1.1所列的三种逻辑门电路的技术参数,试选择一种最合适工作在高噪声环境下的门电路。表题3.1.1逻辑门电路的技术参数表VOH(min)/VVOL(max)/VVIH(min)/VVIL(max)/V逻辑门A2.40.420.8逻辑门B3.50.22.50.6逻辑门C4.20.23.20.8解:根据表题3.1.1所示逻辑门的参数,以及式(3.1.1)和式(3.1.2),计算出逻辑门A的高电平和低电平噪声容限分别为:VNHA=VOH(min)—VIH(min)=2.4V—2V=0.4VVNLA(max)=VIL(max)—VOL(max)=0.8V—0.4V=0.4V同理分别求出逻辑门B和C的噪声容限分别为:VNHB=1VVNLB=0.4VVNHC=1VVNLC=0.6V电路的噪声容限愈大,其抗干扰能力愈强,综合考虑选择逻辑门C3.1.3根据表题3.1.3所列的三种门电路的技术参数,计算出它们的延时-功耗积,并确定哪一种逻辑门性能最好表题3.1.3逻辑门电路的技术参数表tpLH/nstpHL/nsPmWD/逻辑门A11.216逻辑门B568逻辑门C10101解:延时-功耗积为传输延长时间与功耗的乘积,即DP=tpdPD根据上式可以计算出各逻辑门的延时-功耗分别为tPLH+tPHL(11.2)+ns−12DPA=PD=*16mw=17.6*10J=17.6PJ22同理得出:DPB=44PJDPC=10PJ,逻辑门的DP值愈小,表明它的特性愈好,所以逻辑门C的性能最好.3.1.5为什么说74HC系列CMOS与非门在+5V电源工作时,输入端在以下四种接法下都属于逻辑0:(1)输入端接地;(2)输入端接低于1.5V的电源;(3)输入端接同类与非门的输出低电压0.1V;(4)输入端接10kΩ的电阻到地.解:对于74HC系列CMOS门电路来说,输出和输入低电平的标准电压值为:VOL=0.1V,VIL=1.5V,因此有:(1)Vi=02.1V时,将使T1的集电结正偏,T2,T3处于饱和状态,这时VB1被钳位在2.4V,即T1的发射结不可能处于导通状态,而是处于反偏截止。由(1)(2),当VB1≥2.1V,与非门输出为低电平。(4)与非门输入端接10kΩ的电阻到地时,教材图3.2.8的与非门输入端相当于解3.2.2图所示。这时输入电压为VI=(Vcc-VBE)=10(5-0.7)/(10+4)=3.07V。若T1导通,则VBI=3.07+VBE=3.07+0.5=3.57V。但VBI是个不可能大于2.1V的。当VBI=2.1V时,将使T1管的集电结正偏,T2,T3处于饱和,使VBI被钳位在2.1V,因此,当RI=10kΩ时,T1将处于截止状态,由(1)这时相当于输入端输入高电平。

3.2.3设有一个74LS04反相器驱动两个74ALS04反相器和四个74LS04反相器。(1)问驱动门是否超载?(2)若超载,试提出一改进方案;若未超载,问还可增加几个74LS04门?解:(1)根据题意,74LS04为驱动门,同时它有时负载门,负载门中还有74LS04。从主教材附录A查出74LS04和74ALS04的参数如下(不考虑符号)74LS04:IOL(max)=8mA,IOH(max)=0.4mA;IIH(max)=0.02mA.4个74LS04的输入电流为:4IIL(max)=4×0.4mA=1.6mA,4IIH(max)=4×0.02mA=0.08mA2个74ALS04的输入电流为:2IIL(max)=2×0.1mA=0.2mA,2IIH(max)=2×0.02mA=0.04mA。1拉电流负载情况下如图题解3.2.3(a)所示,74LS04总的拉电流为两部分,即4个74ALS04的高电平输入电流的最大值4IIH(max)=0.08mA电流之和为0.08mA+0.04mA=0.12mA.而74LS04能提供0.4mA的拉电流,并不超载。2灌电流负载情况如图题解3.2.3(b)所示,驱动门的总灌电流为1.6mA+0.2mA=1.8mA.而74LS04能提供8mA的灌电流,也未超载。(2)从上面分析计算可知,74LS04所驱动的两类负载无论书灌电流还是拉电流均未超3.2.4图题3.2.4所示为集电极门74LS03驱动5个CMOS逻辑门,已知OC门输管截止时的漏电流=0.2mA;负载门的参数为:=4V,=1V,==1A试计算上拉电阻的值。

从主教材附录A查得74LS03的参数为:VOH(min)=2.7V,VOL(max)=0.5V,IOL(max)=8mA.根据式(3.1.6)形式(3.1.7)可以计算出上拉电阻的值。灌电流情况如图题解3.2.4(a)所示,74LS03输出为低电平,IILtotal()=5IIL=5×0.001mA=0.005mA,有VDD−VOL(max)(54)−VRp(min)==≈0.56KΩIOL(max)−IILtotal()(80.005)−mA拉电流情况如图题解3.2.4(b)所示,74LS03输出为高电平,IIHtotal()=5IIH=5×0.001mA=0.005mA由于VOH(min)

您可能关注的文档

- 《电力电子技术》第四版课后习题解答(清晰版).pdf

- 《电力系统分析》习题集及答案.doc

- 《电力系统分析》第三版(于永源杨绮雯著)课后习题答案中国电力出版社.pdf

- 《电动力学》第三版课后答案.pdf

- 《电动力学》课后答案.pdf

- 《电商概论》课后习题答案.doc

- 《电子商务》试题及答案.docx

- 《电子商务网站建设与维护》章后习题参考答案.doc

- _李中发主编_前六章答案.docx

- 《电子技术基础》第五版(数字部分) 高教(康华光)版 课后答案.pdf

- 《电子技术基础》第五版(数字部分)课后答案 高教 康华光版.pdf

- 《电子技术基础》第五版(数字部分)高教版课后答案.doc

- 《电子测量与仪器》陈尚松版课后习题与答案.doc

- 《电子电路基础》课后习题答案.pdf

- 《电子线路(I)(1到7章)》董尚斌编 课后习题答案(经修改).doc

- 《电子线路练习与单元测试(作业薄式)》参考答案.pdf

- 《电工与电子技术》习题册习题解答.doc

- 《电工学-电子技术-下册》试题及解答(1).doc