- 1.63 MB

- 2022-04-29 14:11:12 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'半导体行业中DRAM的制造与测试—、DRAM器件的基本介绍二、DRAM器件的品圆制造流程三、DRAM器件的封装流程四、DRAM器件的电性测试与良吊率五、DRAM器件晶圆制造的新工艺

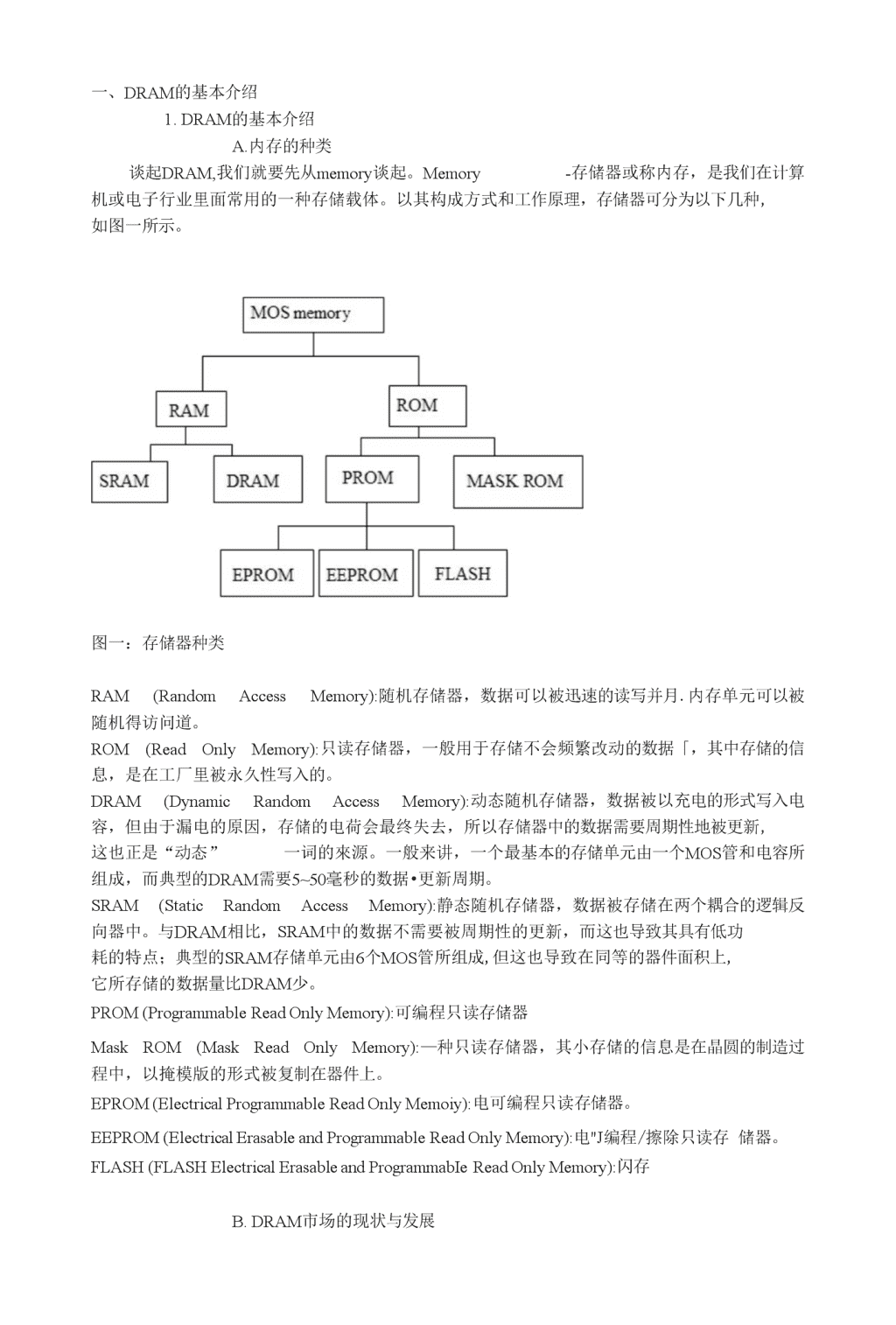

一、DRAM的基本介绍1.DRAM的基本介绍A.内存的种类谈起DRAM,我们就要先从memory谈起。Memory-存储器或称内存,是我们在计算机或电子行业里面常用的一种存储载体。以其构成方式和工作原理,存储器可分为以下几种,如图一所示。图一:存储器种类RAM(RandomAccessMemory):随机存储器,数据可以被迅速的读写并月.内存单元可以被随机得访问道。ROM(ReadOnlyMemory):只读存储器,一般用于存储不会频繁改动的数据「,其中存储的信息,是在工厂里被永久性写入的。DRAM(DynamicRandomAccessMemory):动态随机存储器,数据被以充电的形式写入电容,但由于漏电的原因,存储的电荷会最终失去,所以存储器中的数据需要周期性地被更新,这也正是“动态”一词的來源。一般来讲,一个最基本的存储单元由一个MOS管和电容所组成,而典型的DRAM需要5~50毫秒的数据•更新周期。SRAM(StaticRandomAccessMemory):静态随机存储器,数据被存储在两个耦合的逻辑反向器中。与dram相比,SRAM中的数据不需要被周期性的更新,而这也导致其具有低功耗的特点;典型的SRAM存储单元由6个MOS管所组成,但这也导致在同等的器件面积上,它所存储的数据量比DRAM少。PROM(ProgrammableReadOnlyMemory):可编程只读存储器MaskROM(MaskReadOnlyMemory):—种只读存储器,其小存储的信息是在晶圆的制造过程中,以掩模版的形式被复制在器件上。EPROM(ElectricalProgrammableReadOnlyMemoiy):电可编程只读存储器。EEPROM(ElectricalErasableandProgrammableReadOnlyMemory):电"J编程/擦除只读存储器。FLASH(FLASHElectricalErasableandProgrammabIeReadOnlyMemory):闪存B.DRAM市场的现状与发展

由于DRAM的特性,使其成为在计算机与通讯系统中使用最为广泛的半导体存储器形式。而也因为其制造工艺的先进性,使其成为半导体制造工业的标杆,表一所给出的SIA(半导体产业协会)对半导体产品的产品参数所预测的“路线图”,就是以DRAM器件为代表所给出的。产品年代200120062012线宽(nm)15010050存储器容量1Gb16Gb64Gb逻辑比特/C1M380M2.2B17B芯片尺寸(mm2)4457901580最大连线水平77-89掩模层2324/2628缺陷密度(D/m)875490250芯片接口-I/O"s119519703585晶圆直径(mm)300300450表一:半导体产业路线图—SIA在半导体产业中,DRAM器件的销售利润额为370亿美元(2000年),占整个半导体市场份额的16%。图二给出了DRAM市场利润额的变化图MarketTOqr19941996199?20002DO2Year图二:DRAM市场利润额趋势图由于DRAM制造工艺的不断发展,也使DRAM成为了一种低成本的内存器件,目前,其每个逻辑存储比特的制造成本己小于10-7美元,并且其制造成本还在以每年约26%的速率在继续下降°图三给出了DRAM器件制造成本的下降趋势。

Costperbit冃前的DRAM生产技术己经发展到160nm工艺,每个存储单元的面积可以控制在0.3um2以内。当前主要的DRAM生产商是Samsung,Micro,LG-Hyundai,Hitachi,这几家生产商占到了DRAM市场份额的80%以上。2.DRAM器件的工作原理A.DRAM器件的基本结构谈起DRAM器件的基本结构,我们要先从其最基本的存储单元(MemoryCell)说起,图四为DRAM存储单元逻辑示意图;图五为其存储单元晶圆剖而示意图。从图四我们可以看出,每个DRAM存储单元是由一个MOS管,一个电容,一根字节线(WordLine或称行)和一根比特线(BitLine或称列)所组成的,而这就是典型的DRAMIT(Transistor)lC(Capacitor)存储单元结构(IBM公司于1968年发明)。就是这样一个一个的存储单元组成了DRAM器件存储阵列,而存储阵列一般会占到整个DRAM器件而积的50〜65%,其余的而积主要由外围电路所组成。在每一个存储单元中,MOS管被字节线所控制,起到开关的作用,控制存储单元的读(Reading),^(Writing)与更新(refresh)o在写操作中,电荷从比特线流入并被存储到电荷中;在读操作中,电荷从电容中流出并被反馈到比特线上。从图五中也可以看出DRAM的基本存储单元是如何在晶圆的层叠结构中得以实现的。WordLineWLorRowCommonCellHateCPIConlaxtSNCAccessDKiceCellDielectricNodeSNNodeBitLineContactBLC图四:DRAM存储单元逻辑示意图

BLBLCSNCAccessDevice图五:DRAM存储单元品圆剖曲示意图图六为DRAM器件存储阵列(MemoryArray)简易示意图,从左图可以看出在实际应用的DRAM器件中,使用的是一对比特线(BL/BL),这一对比特线与感应放大^(SA-SenseAmplifier)协作来进行DRAM器件的读操作(这一内容将在后续章节中详细说明)。右图为DRAM器件存储阵列在晶圆上布局的简易示意图,纵向布局的为由多晶硅所构成的字节线,横向布局的为由鹄所构成的比特线和有单晶硅所构成的活性区(AA-ActiveArea)o从此图中的方框可以看出,如果设此器件的最小关键尺寸为F的话,一个DRAM存储单元所占的面积仅为A=4FX2F=8F2,可见,每个存储单元在器件表而上所占的而积是多么小,而这也正是DRAM器件较之其他存储器件存储密度大的原因。A卅=A=n卜AA卅HFlAAWL1WL2WL3WL4WL5WL6WL1BL|fft4-J1丿A=4FX2F=SP图六:DRAM器件存储阵列简易示意图。图七所是的为在实际应用小的DRAM存储单元,其上图为通过电子扫描电镜(15.0Kev,X15.0K)所照取的器件剖面图,其下图为DRAM存储单元逻辑俯视图。通过其对应关系可以看出,外面用红色虚线勾勒岀来的为存储单元的存储节点(即为电容),里面用黄色虚线勾勒出來的为由多晶硅所构成的MOS管的栅极。从上图我们也可以清楚地看出DRAM器件中的隔离区(LOCOS-LocalOxide,局部氧化隔离区),由第一层金属层(Metal1-^)所构成的比特线,由第二,三层金属层(MeUil2,3■铝)所组成的互连线(interconnect)和四层多晶硅所组成的电容。

图七:DRAM存储单元示意图让我们从更近的角度来看DRAM器件的存储单元,图八为DRAM存储单元的放大示意图,器件内部的氧化物已被溶剂(BOE溶剂)去除掉,我们可以更清楚地看到上面的电容,中间的比特线和下面的字节线。图八:DRAM存储单元的放大示意图

下而我们再来看DRAM器件的存储阵列。我们以IBM公司的256MbDRAM为例,图九所示为其实际器件俯视图与其逻辑示意图之间的对应关系;图十所示为其实际器件俯视图与实际器件剖面图之间的对应关系。从中我们可以看出,DRAM器件的存储阵列主要就是由字节线和比特线组成的矩阵网络所串起的海量存储单元所构成的。SAbankSAbalkSAtankSAbankSAbank■SAbank需器/BitlineSAbankSAbankSAbankBitliWordline:点4A―*1-h-<|:Ah/A■IA4ASAbankPenphcrycircuits图九:DRAM器件俯视图与其逻辑示意图之间的对应关系SAbankSAbankSAbankSAbankSAbankSAbankSAbankSAbankSAbankSA^bankSAbank/Bitlin、BitlinecontactWordPeripherycircuits图十:DRAM器件俯视图与剖血图之间的对应关系那么,DRAM器件的外围电路又是如何组成的呢?图十一为DRAM器件的简易逻辑示意图,从中我们可以看出DRAM器件的外围电路主要是由行地址解码器(RowAddressDecoder)>列地址解码器(ColumnAddressDecoder)>行输入缓冲器(XInputBuffer)列输入缓冲器(YInputBuffer)、写驱动器(WriteDriver)输入/输出口(DeviceI/O&Buffer)和感应放大器(SenseAmplifier)所组成。行、列地址解码器的作用是当外部发出指令要对某一存储单元进行读/写操作时,它们对外部指令中的行、列地址进行解码,以得出DRAM器件内部存

储阵列的地址,进而控制字节线和比特线,将其打开,从而对指定的存储单元进行读/写操作。感应放大器的功能将在后续章节中详细说明。Read/WriteChipenable图十一:DRAM器件简易逻辑示意图B.DRAM器件的工作原理在这一章节中,我们将主耍从四方面介绍DRAM器件的工作原理,它们是DRAM器件的写操作,读操作,感应放大和数据更新,下面先让我们从DRAM器件的写操作开始。DRAM器件的写操作工作原理相对容易理解,请见图十二,从图中我们可以看出,存储单元-电容的一个极板上始终都被加上Vcc/2的电压,而当要对某一存储单元进行写操作时,这一存储单元的字节线上会被加以电压Vccp(Vccp>Vcc+Vt),这一电压会被加到这一存储单元开关MOS管的栅极上,这一电压大于MOS管的开启电压,这样,MOS管导通,就可以对这一存储单元进行写操作了。当要写入1时,比特线上会加以电压Vcc,而这一电压会通过导通的MOS管,由其源极传导到漏极并最终加到存储电容的另一极板上(如左图所示);与此类此,当要写入0时,则加以电压Ov(如右图所示)。存储单元中所储存的数据是0还是1,由电容两极板间的电压差方向所定。当存储单元被执行写操作以后,其存储电容上所储存的电荷电量由公式Q=C*V=Ccell*Vcc/2o我们会在下面的章节中说明,存储电容上所储存的电荷电量Q越大,其维持漏电的时间也就越长,而数据更新所需的周期也就越长,这样也就可以使器件减少功耗,而从上面的公式也可以看出,要想增大Q,增大电容的容值,是唯一实际可行的办法(增大Vcc反而会增加功耗),而在后面将要说明的DRAM器件的读操作中,增大电容容值,也会使得DRAM器件在读取数据时更加容易和准确。在本文的第二章中,我们会介绍在DRAM器件晶圆的制造的过程小,在工程上是如何通过增大电容的极板面积从而实现增大其电容容值的。

VccVccp>Vcc^VtVcc/2~^VccStore“1"图十二:DRAM器件写操作示意图。下面,我们将阐述DRAM器件的读操作和感应放大。在DRAM器件进行读操作时,进行读操作的存储单元的字节线被打开,原先存储在电容中的电荷被释放岀,由于此存储单元的开关MOS管已被字节线打开,这样,释放出的电荷会通过MOS管继而释放到比特线上,由于存在由比特线所产生的等效电容,所以,在电容电荷释放过程中,所产生的电圧变化由以下公式得出。DRAM器件就是根据这一电压变化的方向来判定其存储单元中所存储的数据是0还是loAV=(V(x/2)Cc«nBLZZZI"1~Cbl~|~c“u图十三:DRAM器件读操作示意图但是,还有一个问题,让我们举一个例子来说明:假设我们的DRAM器件的工作电压为Vcc=3.3v,电容容值为Ccell=50fF,比特线的等效电容为CBL=300fF,电容小所存储的电荷电量Q=CV=dV*(Ccell+CBL)=(Vcc/2)*Ccell,这样,我们可以得出,在电容放电的过程中,电压的变化量为dV=(3.3⑵*[50/(300+50)]=0.236v。一般来讲,目前DRAM器件的dV也就是在80〜200mv之间。这样小的电压变化量,DRAM器件很难在读取数据•的时候准确判断出存储的数据到底是0还是1,而这也就是我们需要在DRAM器件小加入感应放大器的原因。感应放大器(SenseAmplifier)的工作原理请见图十四,其工作电路示意图请见左图,工作过程示意图请见右图。简而言之,它的功能就是将DRAM器件进行读操作时所产生的“微小”的<1,放大成工作电压Vcc。举例说明,如果存储单元小所储存的数据为1,在进行读操作时,字节线的电压首先被拉高到Vccp,存储单元开关MOS管被打开,此存储单元处于读/写激活状态,然后一对比特线与Vcc/2电压断开,继而,在读出1时,BL线上产生了正向的dv电氐此电压导致右下角的NMOS管被开通,使得N节点上的负电压加在了BL线上和左上角PMOS管的栅极上并使其导通,最终,P节点上的Vcc电压就通过此MOS管加在了BL线上,这样,外部器件就可以容易而准确地根据一对比特线上的电压差是十Vcc还是・Vcc来判断出存储单元中储存的数据是0还是1。

PSANSA-3L•YaTime图十四:DRAM器件感应放大器工作原理示意图最后,再让我们看一下DRAM器件的数据更新(Refresh)。由于DRAM器件器件的数据存储主要是由电容所完成的,而由于电容和开关MOS管的漏电流,使得电容中所存储的电荷很快就会漏光,这样,就需耍我们周期性地对每个存储单元进行数据更新以阻止这样的现象发生。周期性的数据更新其实很简单,就是对存储单元进行一次读/写操作,把读出的数据原样再写回去。目前,市场上大多数的DRAM器件的数据更新周期在5〜50ms之间,一些新的DRAM器件甚至可以延长到100~200ms。3.DRAM器件的芯片介绍A.DRAM器件的管脚介绍让我们先从简单的1KbDRAM器件开始对其芯片进行介绍。图十五为1kbDRAM器件功能管脚示意图,其中所示的为DRAM器件工作所必需的一些管脚,女匕电源管脚(Vss,Vdd),片选管脚(CE),读/写控制管脚(R/W),数据输入(Din)和输岀管脚(Dout)以及行、列地址输入管脚(R1〜R5,C1〜C5)。因为其各有5个行、列地址管脚,所以它所能控制的内存大小为(25)2=io24b,即为1Kb。图十六为其内部逻辑电路示意图,因其内部工作原理己在上一章中进行了讨论,在这里就不再赘述了。]16C3Jl5GJl4C5]13CEDom斤57[Hi8(2]11D駅JlOVss]9怯图十五:1kbDRAM器件功能管脚示意图

图十六:lkbDRAM器件逻辑电路示意图B.DRAM器件工作时序图十七,十八和十九分别描述的是DRAM器件读,写和数据更新操作的工作时序,因其工作原理己在上一章中论述过,在此就不再重复了。在这里需要说明的是其中的一些时域参数:tRC(Readcycletime):读操作周期lAC(Accesstime):访问时间twc(Writecycletime):写操作周期tAW(AddresstoWritedelaytime):写激活与地址输入之间的时间延迟tWP(Writepulsewidth):写脉冲宽度C£=0图十七:DRAM器件读操作工作时序图

CE图十八:DRAM器件写操作工作时序图图十九:DRAM器件数据更新工作工作时序图二、DRAM器件的品圆制造的工艺与流程IC产品的晶圆制造工艺非常复杂,以目前市场上主流的64MbDRAM为例,它的生产工艺中需要4层多晶硅、3层金属互连层,需要8次CMP工艺,21层光照掩模,这样的一个DRAM器件在其晶圆制造过程小大约需要总共300多步工艺。在业界中,为了以示区分,将IC产品的晶圆制造工艺分为了前段和后段:前段主要包括了底层器件的制造工序;后段以金属互连层的制造工序为主,在本文中,我们也将按照前段、后段逐一加以论述。在这一章中,为了论述方便,我们还加入了大量晶圆剖面示意图来说明DRAM器件的晶圆制造工艺,在这些示意图中,左图显示的是存储阵列的结构而右图显示的是外围电路的结构。1.DRAM器件晶圆制造的前段工艺首先,我们需要的单晶硅基材类型为(100)晶向,单位面积电阻为10+/・1.5ohm的P型硅片,并且要在上而生长出7um的外延层(Epi)。接着,会在晶圆上在900C的温度下生长出100A的二氧化硅层(生长这一层二氧化硅的目的是为了避免应力很大的SiN将下面的单晶硅晶格压坏),然后再在其上在760C的温度下淀积一层1500A的SiN,随后再在其上涂敷光阻

以对SiN层进行刻蚀,如图二十所示。在对SiN刻蚀后,再以其为掩模版,继续对硅片进行刻蚀,深度大约为3700A,以形成AA(活性区)之间的STI(ShallowTrenchIsolation,浅沟道隔离槽),如图二十一所示。所最终形成的AA/STI如图二十二中的电子扫描电镜的照片所示。PHE-OXHXP-TOESUBSTRA.TECELLARRAYCROSSSECTDNAAPhoQPRXLA.SKPEE-OXTEEPEKIFHEFLALCROSSSECTIO<图二十:AA(ActiveArea)区域刻蚀Hardmask(SiN)的形成SiNSiNSZw人・MNPHE-OXIEEP-TOESUBSTRATESTISTIPHE-OXITESTICELLARRAYCROSSSECTDNPERIPHERALCROSSSECTKK图二十一:STI(浅沟道隔离槽)的形成图二十二:AA/STI俯视图下一组工艺的目的是向STI重点及二氧化硅以最终形成AA区域之间的隔离层。首先是用HDP(HighDensityofPlasma,高密度等离子体)工艺在整片晶圆上淀积硅的氧化物,如图二十三所示。然后,再使用CMP(ChemicalMechanicalPolish,化学机械抛光)工艺将多余的SiN和二氧化硅磨去,这样就最终完成了STI中氧化隔离物的充填,如图二十四所示。

HEPFillCEILAREAYCROSSSECTONPERIFHER.ALCROSSSECTICK图二十三:HDP淀积后的STISTISTIPKE-OXIIXP-TOESUBSTRATESTISTISTIPKE-OXIEECEILARRAYCROSSSECTONPEKffHEJLALCROSS巫CTI®图二十四:填充后的STI下一组工序主要是通过Implant(离子注入)工艺以形成器件中的N井与P井。在离子注入之前,为了防止大能量注入的离子对下面的单晶硅的晶格造成损伤,需要在品圆上生长一层牺牲氧化物(SacrificeOxide)(800C,50A),这层氧化物会保护下面单晶硅的晶格,其会在离子注入以后被除去(顾名为牺牲氧化物)。在牺牲氧化物生长完成后,以光阻为掩蔽物,依次进行外围电路的N井和P井的离子注入,如图二十五,二十六所示;和存储阵列的N井和P井的离子注入,如图二十七所示。图二十五:外围电路N井的离子注入(P1M150E3T00,磷离子注入,注入能量为1M电子伏特,注入密度为1.5X10E13/CM3,注入角度为垂直(0度角)注入)STIN-WeCSTIP.ZSTIPERIPHERALCROSSSECTICK图二十六:外围电路P井的离子注入(BI80K150E3T07,硼离子注入,注入能量为180K

电子伏特,注入密度为1.5X10E13/CM3,注入角度为偏离法线角7度(7度角)注入)图二十七:存储阵列N井和P井的离子注入(P1M150E3T00,磷离子注入,注入能量为IM电子伏特,注入密度为I.5XI0EI3/CM3,注入角度为垂直(0度角)注入;B180K300E2T07,硼离子注入,注入能量为180K电子伏特,注入密度为3.0X10E12/CM3,注入角度为偏离法线角7度(7度角)注入)下一组工序主要包括了形成MOS管栅极氧化物的工艺。在淀积多晶硅之前需要先生长栅极氧化物,在800C的温度下,用湿法工艺生长一层77A厚的氧化物薄膜。然后再在530C的温度下,淀积800A的多晶硅层,随后再在565C的温度下淀积1000A的WSi(硅和钩的合金)(淀积WSi的冃的是为了减少以后Metal1和栅极连接时的连接电阻(ContactResistance)0在其上再用PE(PlasmaEnhancement,增强型等离子体)工艺淀积SiON(400C,580A),这一层是做为后续光刻(Photo・Etch)曝光(Expose)工艺中的防反射层(ARC-AntiReflectionCoat)。最后一层是在760C温度下,淀积1320A厚的SiN层,这一层的目的是保护下面的栅极,最终的结果如图二十八所示。随后,还有两步退火工艺:一步为在800C温度下,N2的环境中,60分钟的退火工艺,这一步是为了使多晶硅与WSi形成合金,以降低阻值;另一步是在1000C的温度下,N?的环境中,30秒的快速热退火工艺(RTA-RapidThermalAnneal),这一步工艺的目的是为了修复在前步离子注入工艺中所伤害的单晶硅晶格。最后,为了形成栅极,需要用两步光刻工艺对以上各层进行刻蚀(第一步刻蚀SiN,SiON;第二步刻蚀WSi,Poly),所最终形成的栅极如图二十九所示。从以上工艺中可以得知,在这种DRAM器件的晶圆制造工艺中,栅极是由四层所组成的(Poly+WSi+SiON+SiN),图三十给出了各层的厚度,它们统称为栅极堆栈(GateStack)«图三十一给出了栅极形成后的俯视图,横向亮白的区域为活性区(AA),纵向黑色的为栅极。CELLARRAYCROSSSECTDNPERIFHER.ALCBDSSSECTICK图二十八:栅极的淀积

STIP・ZSTIf■―CEILARRAYOtOSSSECTDNPERIFHER.ALCROSSSECTICK图二十九:栅极的形成Poly/W^Gate(P1L)图三十:栅极堆栈(GateStack)的组成图三十一:AA与栅极的俯视图下面的工序包括了MOS管源漏极形成的工艺。首先使用在700C的温度下,N?的环境中,30秒的快速热退火工艺(RTA),这一步RTA工艺是为了修复在前步栅极刻蚀中所伤害的单晶硅的晶格。下一步是使用离子注入工艺(P020K250E3T00,磷离子注入,注入能量为20K电子伏特,注入密度为2.5X10E13/CM3,注入角度为垂直(0度角)注入)形成轻掺杂的源®®(LDD-LightlyDopenDrain),如图三十二所示。随后的工艺是形成Spacer,Spacer对栅极堆栈形成绝缘保护,减少其应力,同时也是为了在后步源漏极离子注入中最终形成优化的源漏极轮丿郭产生作用。其形成工艺如下:首先在760C的温度下,在晶圆上淀积一层500A的SiN,然后再对其进行光刻,所最终形成的形状如图三十三所示。再Spacer形成后,就可以为源漏极的最终形成进行重度掺杂了,首先用离子注入工艺对PMOS管的源漏极进行掺杂(BF025K500E5T00,硼氟离子注入,注入能量为25K电子伏特,注入密度为5X10E15/CM3,注入角度为垂直(0度角)注入);然后再对NMOS管的源漏极进行掺杂(As015K430E5T00,W离子注入,注入能量为15K电子伏特,注入密度为4.3X10E15/CM3,注入角度为垂直(0度角)注入),所最终形成的源漏极如图三十四所示。

、CEILARRAY50SSSECTDNSTI图三十二:LDD(轻掺杂的源漏极)的形成CELLARRAYCROSSSECTDK图三十三:Spacer的形成。sti丿JPZ!PERIFHErLALCEOSSSECTICKCELLARRAYCROSSSECTDN图三十四:源漏极的形成下面的丁.序是在晶圆上淀积硼磷玻璃(BPSG-BoronPhosphorusSiliconGlass)。首先在480C的温度下淀积8500A的硼磷玻璃,由于器件表面栅极的存在,使得淀积后的晶圆表血并不平整,为解决这一问题,需要在800C的温度下,N2的环境中,对品圆表面进行60分钟的回流(Reflow)T整化,回流前后晶圆表而的变化请见图三十五。在回流后,硼磷玻璃的厚度大致会减少到7800A左右,然后再用CMPI艺将其最终平整到5800A左右,请见图三十六。

Asdeposit.Afterreflow图三十五:回流前后硼磷玻璃表面的比较庄FJffiERALCROSSSECTICK图三十六:淀积硼磷玻璃下面的工艺是为了形成源极与电容、漏极与比特线(Metal1)之间的连接孔。首先使用光刻工艺将源漏极上方的硼磷玻璃刻蚀掉(图三十七为刻蚀后的俯视图),然后再在53OC的温度下在晶圆上淀积3000A的多晶硅,最后再利用CMPT艺将连接孔以外的多晶硅磨去,这样就最终形成了连接孔,如图三十八所示。图三十七:源、漏极与电容、比特线间连接孔刻蚀后的俯视图

CELLARRAYCROSSSECTDNPEKIfflErLALCROSSSECTICK图三十八:源、漏极与电容、比特线间连接孔的形成下面的一组工序是DRAM器件晶圆生产过程中最核心的工艺即存储单元电容的形成。第一步是在品圆表-血继续淀积23500A的硼磷玻璃,随后还是冋流平坦化工艺(800C温度,Nr20分钟),然后再利用光刻工艺对其进行光刻以为以后电容的形成留出空间,刻蚀后的深孔直径大约为0.28um,如图三十九所示,深孔刻蚀后的俯视图如图四十所示。第二步是形成电容的一个极板:首先在530C的温度下,在晶圆上淀积300A的多晶硅,这层多晶硅也会附着在深孔的周壁上,然后再在其上在568C的温度下,淀积530A的Rugged-Poly,这层Rugged-Poly也就是电容的第一个极板,而淀积Rugged-Poly的目的也正是向前文所论述到的那样,是为了增加电容极板的表面积,此时,我们需要将晶圆表面上深孔以外区域上的多晶硅与Rugged-Poly除去,在这里,我们使用的是CMP工艺,但在CMP之前,我们需要在晶圆表而上(主要是为了在深孔中,以防止CMP磨出的残渣落入深孔而无法清除)涂敷光阻,然后再进行CMP,CMP后的俯视图如图四十一所示。在将多余的多晶硅与Rugged-Poly清除后,第三步工艺是淀积电容的介质,介质主要由硅的氧化物和氮化物所构成,厚度达约为250A,此时所形成的结构如图四十二所示。最后一步工艺是形成电容的另一个极板,首先在530C的温度下,淀积720A的多晶硅以作为电容的另一个极板,最后再使用光刻将多余部分的电容介质和多晶硅刻蚀去掉,以将电容一个一个分离开。所最终形成的电容结构如图四十三所示。CEILARRAYCROSSSECTDNPERIPHERALCROSSSCTICK图三十九:深孔刻蚀后的剖视图

图四十:深孔刻蚀后的俯视图图四^一:多品硅与Rugged-PolyCMP后的俯视图CdlCEU.AREAYCROSSSECTDN图四T•二:多晶硅、Rugged-Poly和电容介质淀积后的结构示意图

CELLAKPAYCROSSSECTKJNSTISTI丿Jsn■N-WeC.1~PZ!PERIPHERALCROSSSECTICK图卩q十二:电容结构不意图下一组工序包含了比特线(Metal1,第一层金属连线)以及其与下面的器件之间连线的形成。第一步工序是形成连线:首先是在晶圆表而上再淀积2500A的硼磷玻璃,然后在800C的温度下,N2的环境中,对其进行20分钟的回流平整化,随后再通过光刻工艺刻蚀出Metal1与下面器件间的连接孔,此时形成的器件结构如图艸十舛所示,图艸十五为其俯视图;第二步工序是产生Metal1,同时在淀积Metall的同时也会填充已刻蚀好的连接孔,首先先通过CVD(ChemicalVaporDeposition,化学气相淀积)工艺淀积约350A的Ti/TiN,这一层淀积的目的是为了形成为以后钩的淀积而作铺垫的胶连层,然后再在450C的温度下,通过CVD工艺淀积1000A的钩作为Metal1的主体,接着再在380C的温度下,通过增强型等离子体工艺(PE-PlasmaEnhancement)淀积310A的SiON作为以后Metal1刻蚀的防反射层(ARC-AntiReflectionCoat),最后再对Metal1进行光刻以形成金属连线,所最终形成的结构如图四十六所示。CEIL.AKRA.YCROSSSECTDNPERIPHERALCROSSSECTKK

图四十四:Metal1与底层器件间连接孔的形成

图四I•五:Me(all与底层器件间连接孔的俯视图CELLARKAYCROSSSECTONPEPJffiEP-ALCPOSSSECTICK图四十六:Metal1与底层连接线的形成'

您可能关注的文档

- 2019年半导体行业发展趋势

- 半导体行业研究

- 半导体行业观察系列二十:AMAT,Q4业绩符合公司预期,未来展望乐观

- 半导体行业国产替代系列九:离子注入机,四大核心装备之一,迎来国产替代机遇

- 半导体行业景气周期专题报告:多重创新周期叠加,恰逢2020

- 半导体行业全球半导体观察(11月):数据中心回暖,5G出货量指引好于预期

- 半导体行业深度报告(系列之一):成长与迁移,全球半导体格局演变

- DB32T 3747-2020 半导体行业污染物排放标准.docx

- 半导体行业分析报.ppt

- 半导体行业专业词汇.doc

- 半导体行业的客户满意度研究——以C公司为例.pdf

- 一文看透中国半导体行业现状.doc

- 半导体行业职位招聘表.doc

- 半导体行业名词解释.doc

- 行业梳理:电子元器件子行业——半导体行业.doc

- 机器视觉系统在半导体行业的应用.doc

- 半导体行业专用仪器.doc

- 半导体行业专业知识 wafer知识.doc